# Systematic Identification of Key Design Factors for Chiplet Eco System Enabling

Thomas To, Ph.D., AMD Fellow 5/11/2022

# Speaker

Thomas To, PhD, AMD Inc.

Thomas is an AMD Fellow focusing on System Memory & IO Platform Architecture Development. Prior to AMD's acquisition of Xilinx, Thomas was a Distinguished Engineer in System Memory Signal Integrity group. Before joining Xilinx, Thomas was a principal engineer in NVIDIA Advanced Technology Group focused on highspeed circuits & system channel designs. Before NVIDIA, Thomas worked for Intel for more than 16 years covered and led many different types of system memory IO development. Thomas received his PhD degree in Electrical Engineering from the Ohio State University in 1995 & he is the inventor of over 38 patents in the fields of mixed signal IO circuits and system memory configurations as well as high speed clocking for highspeed memory designs.

## **Abstract**

With so many features of interest at play in computing, adding all the features of interest in the most advanced silicon process node to meet the ever-growing computing demand is very challenging. Chiplet implementation uses a selection of modular dies, referred to as chiplets, to provide a heterogeneous integration approach and to offer best-in-class feature combination. However, identifying the key system design factors to enable a successful system is complicated.

In this talk, a design factor sensitivity methodology will be presented. Chiplet system channel jitter is used as the desired optimized result and the impacts of different design factors on the result are examined. Based on a behavior jitter model, this method first correlates the model to an actual measurement of a High Bandwidth Memory (HBM) system.

The model is then extended to represent different input factors for the system output data path jitter. These input factors include the multiple supply power frequencies, their corresponding noise amplitudes, signal transition slew rate, as well as channel routing configurations such as different ground signal configurations. A set of output jitter response surface model, with different power tone frequencies and noise amplitudes, is then developed, with an optimal channel interconnect. The response surface model provides a contour to identify critical input parameters such that system platform designers can evaluate the effects of multiple input factor and their interactions. This approach allows for a holistic consideration for optimizations & specification.

- Background

- ASIC Development Costs and Return of Investment Trends

- Overview of Chiplet Integration as a Solution & its Challenges

- Chiplet Connection

- What are the key design factors?

- How to determine these key design factors for development design & for specification?

- Design Factors (Specification Parameters) Sensitivity Analysis

- Unified System Jitter Model for Design Factor Gradient Quantification.

- A Case Study: Performance Evaluation based on Input Design Factor Sensitivity Results

- Summary and Conclusions

- Background

- ASIC Development Costs and Return of Investment Trends

- Overview of Chiplet Integration as a Solution & its Challenges

- Chiplet Connection

- What are the key design factors?

- How to determine these key design factors for development design & for specification?

- Design Factors (Specification Parameters) Sensitivity Analysis

- Unified System Jitter Model for Gradient Descend Quantification.

- A Case Study: Performance Evaluation based on Input Design Factor Sensitivity Results

- Summary and Conclusions

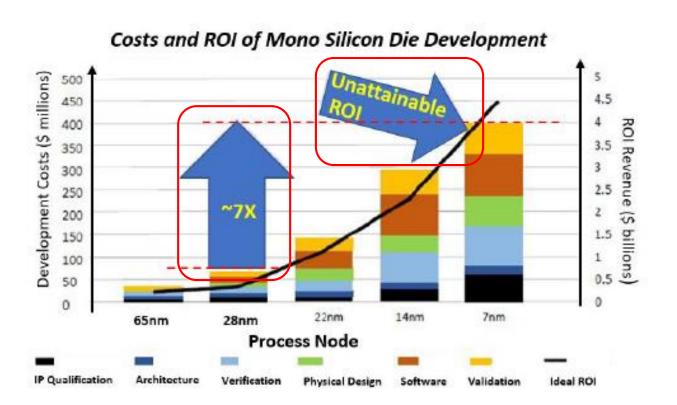

# ASIC Development Costs and Returns of Investment Comparison

- → The cost of monolithic IC integration and scaling has skyrocketed in recent years as the process node shrinks.

- → The Return of Investment of monolithic IC compared to its development cost is unattainable for process node of 7nm and beyond.

- → Adding all the features of interest in one IC and one process node, increases complexity and cost.

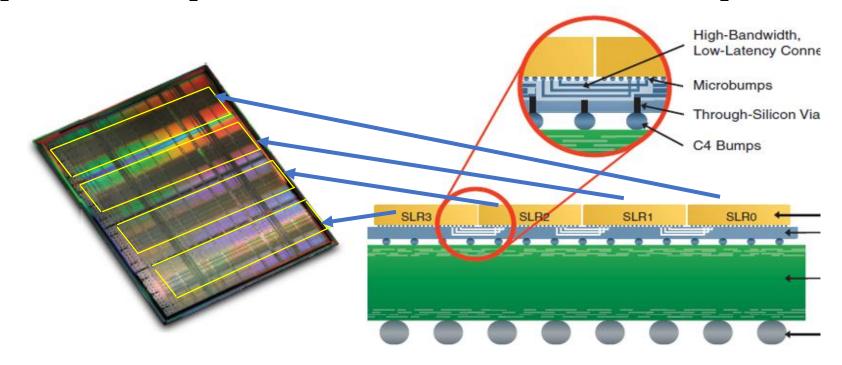

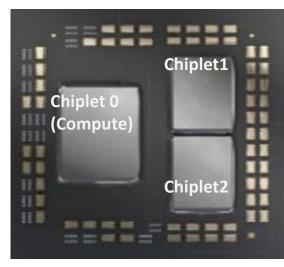

## **Chiplet Implementation Example**

- → Chiplet implementation uses a selection of modular dies called chiplets.

- → Chiplets may have different functions and can be developed on different process node.

- → Mix and match of chiplets can meet the feature and performance needs.

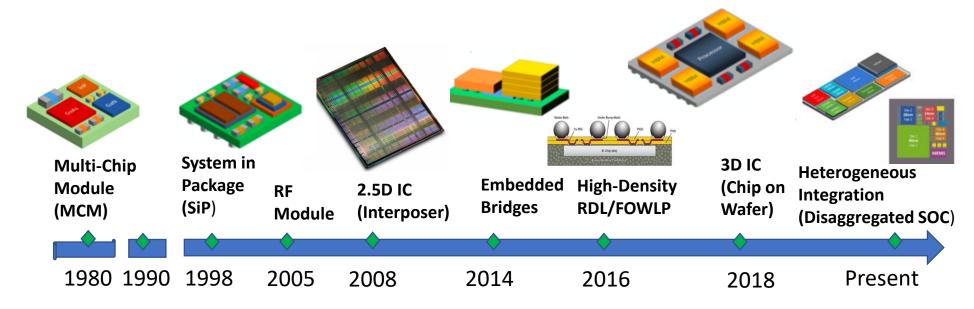

## **Chiplet Integration TimeLine**

- → Chip to Chip integration has been continuously evolving and accelerating the revolution.

- → More Development Challenges from many different aspects, such as

- → Combining 3<sup>rd</sup> party design & Optimize Completed System Holistically.

- → How to identify and quantify key design factors that matter?

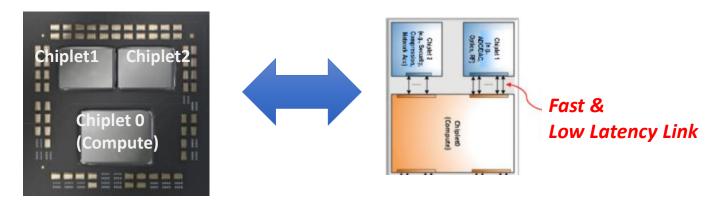

# **Chiplet Connection/Integration Challenges**

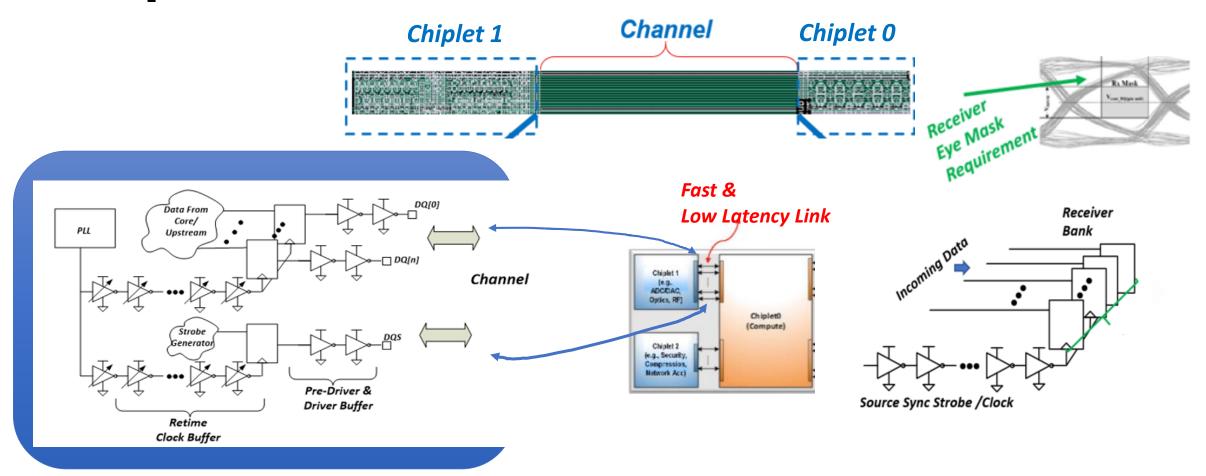

High Speed/Bandwidth Data Transmission between the chiplets -> Low Latency & High Throughput

- → Chiplets can be developed by One or Multiple Companies.

- → Optimized System Integration requires Identification of Critical Design Factors.

A Unified Chiplet Interconnect Jitter Analysis Approach:-

- → Combined System Jitter from Tx to Rx serves as the Figure of Performance Merit.

- → Model is based on analytical expression of power supply induced jitter and jitter accumulation along the path.

- → The sensitivity of each Design Factors will be quantified and compared.

- Background

- ASIC Development Costs and Return of Investment Trends

- Overview of Chiplet Integration as a Solution & its Challenges

- Chiplet Connection

- What are the key design factors?

- How to determine these key design factors for development design & for specification?

- Design Factors (Specification Parameters) Sensitivity Analysis

- Unified System Jitter Model for Gradient Descend Quantification.

- A Case Study: Performance Evaluation based on Input Design Factor Sensitivity Results

- Summary and Conclusions

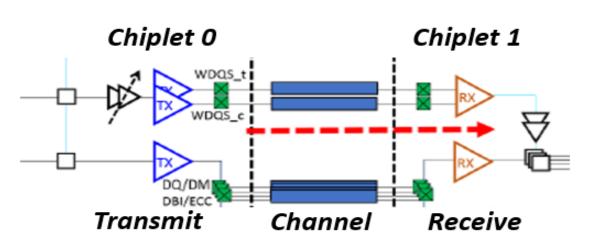

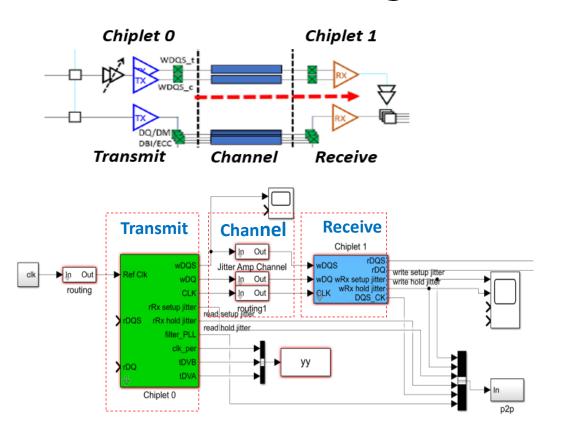

## **Typical Chiplet Connection**

- → Chiplet Connection Transmit Speed ties to how to control link Jitter.

- → Jitter at each stage is integrated with the previous stage jitter as input.

- → Jitter output is an Accumulative Jitter number.

## **Chiplet Connection Link Factors**

- → Data Transmit has Multiple Stages of Induced Jitter & Accumulation from end to end.

- → Jitter has many underlining contributed factors such as power noise etc.

- Background

- ASIC Development Costs and Return of Investment Trends

- Overview of Chiplet Integration as a Solution & its Challenges

- Chiplet Connection

- What are the key design factors?

- How to determine these key design factors for development design & for specification?

- Design Factors (Specification Parameters) Sensitivity Analysis

- Unified System Jitter Model for Gradient Descend Quantification.

- A Case Study: Performance Evaluation based on Input Design Factor Sensitivity Results

- Summary and Conclusions

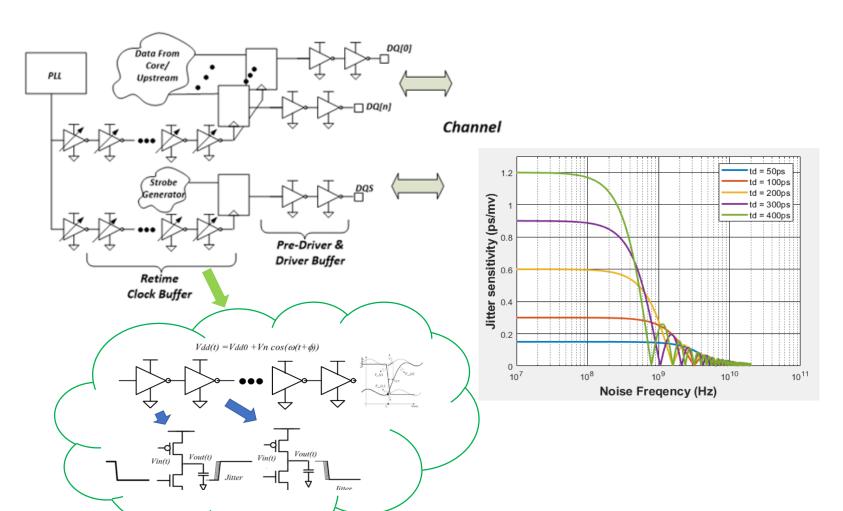

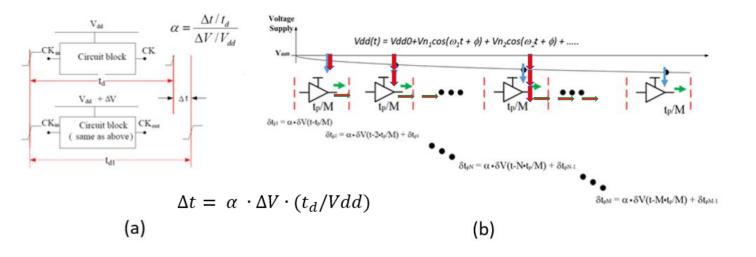

### **Power Noise to Jitter Transfer**

- → Relatively constant jitter sensitivity below a certain noise frequency.

- → Above knee frequency the response of buffer is not fast enough.

- → A longer delay clock buffer has higher jitter sensitivity.

- → Noise Tone Frequencies, Noise Tone Amplitudes, Buffer Delay and Process Characteristic are the Critical Factors.

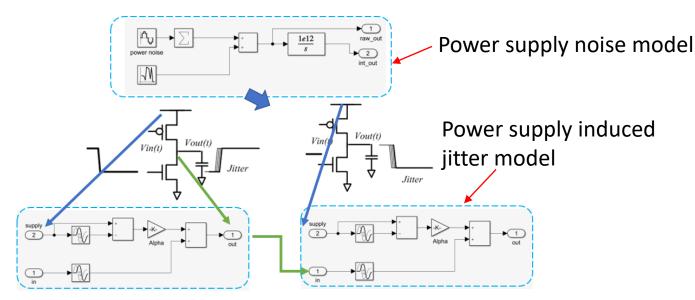

### Power Noise Induced Jitter & Accumulation

- → Power Noise Modulates the Buffer Delay.

- → Each Stage experiences different Noise and will induce Jitter accordingly.

- → Each Stage will also accumulate Jitter.

- → A First Stage Buffer with Power induced Jitter model.

- → Power noise can be modeled with different Noise Frequencies and Amplitudes.

- → Jitter of first stage is added to next stage.

→ Design2

Design1

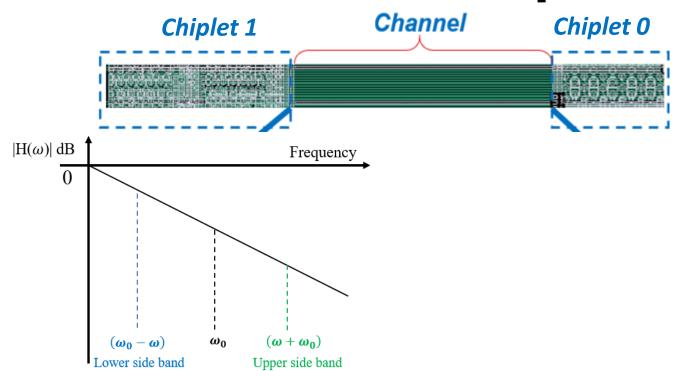

# **Channel Jitter Amplification**

1.2 **Jitter Amplification Factor** 1.15 1.1

$F_{SJ}(\omega) = \frac{1}{2} \left| \frac{H(\omega + \omega_0)}{H(\omega_0)} + \frac{H(\omega - \omega_0)}{H(-\omega_0)} \right|$

- → Transfer function of a Lossy Channel decays with Frequency.

- → Jitter passing through a Lossy Channel amplifies due to higher Attenuation at Higher Sideband.

- → Design1 is a Silicon Interposer channel.

- → Design2 is an InFO media Channel.

1.05

0.95

0

→ Interconnect Choice shows Different Characteristics

**Noise Frequency (GHz)**

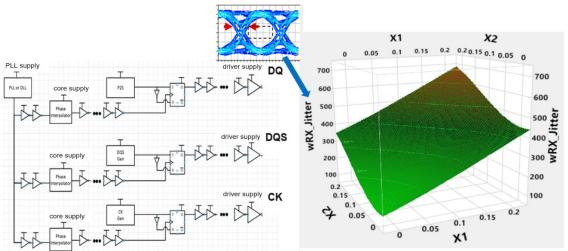

# **Combined System Jitter Model**

- → Unified model is used to create response surface model using critical input factors.

- → The sensitivity of gradient of each input factor is studied and optimized.

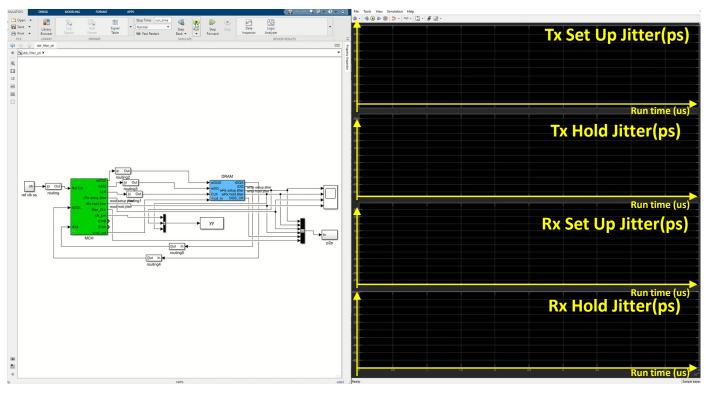

### **Unified Jitter Model Correlation**

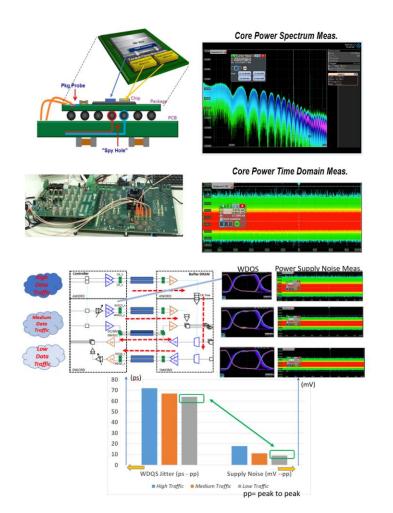

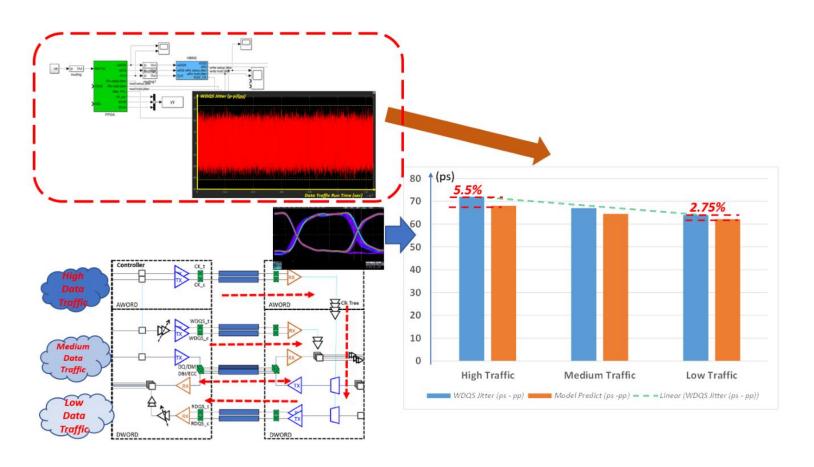

- → System Jitter Measurements with different traffic excitations.

- → System Jitter Model predicted peak to peak jitter with different traffic excitations

- & show reasonable match.

# Input Design Factors Generation of Training Examples

- → Integration involves different IP from Different Companies

- → System Design needs to guarantee Targeted Performance

- → System Design needs to Identify Critical Factors for Optimization

$$y=b_0+\sum_{i=1}^n b_i x_i + \sum_{j=1}^n \sum_{k=1}^n b_{jk} x_j x_k + \epsilon$$

|                         | <i>x</i> 1                    | X2                            | х3                            | X4                            |   | X14                            | X15                            |

|-------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|---|--------------------------------|--------------------------------|

| yı                      | x <sub>1</sub> <sup>(1)</sup> | x <sub>2</sub> <sup>(1)</sup> | x <sub>3</sub> <sup>(1)</sup> | x <sub>4</sub> <sup>(1)</sup> | : | x <sub>14</sub> <sup>(1)</sup> | x <sub>15</sub> <sup>(1)</sup> |

| <i>y</i> <sub>2</sub>   | :                             | x <sub>2</sub> <sup>(2)</sup> | :                             | :                             | : | :                              | :                              |

| уз                      | :                             | :                             | x <sub>3</sub> <sup>(3)</sup> | :                             | : | :                              | :                              |

| :                       | :                             | :                             | :                             | :                             | : | :                              | :                              |

| :                       | :                             | :                             | :                             | :                             | : | :                              | :                              |

|                         | :                             | :                             | :                             | :                             | : |                                | :                              |

| <i>y</i> <sub>m-1</sub> | :                             | :                             | :                             | :                             | : | $x_{14}^{(m-1)}$               | :                              |

| $y_m$                   | :                             | :                             | :                             | :                             | : | :                              | $x_{15}^{(m)}$                 |

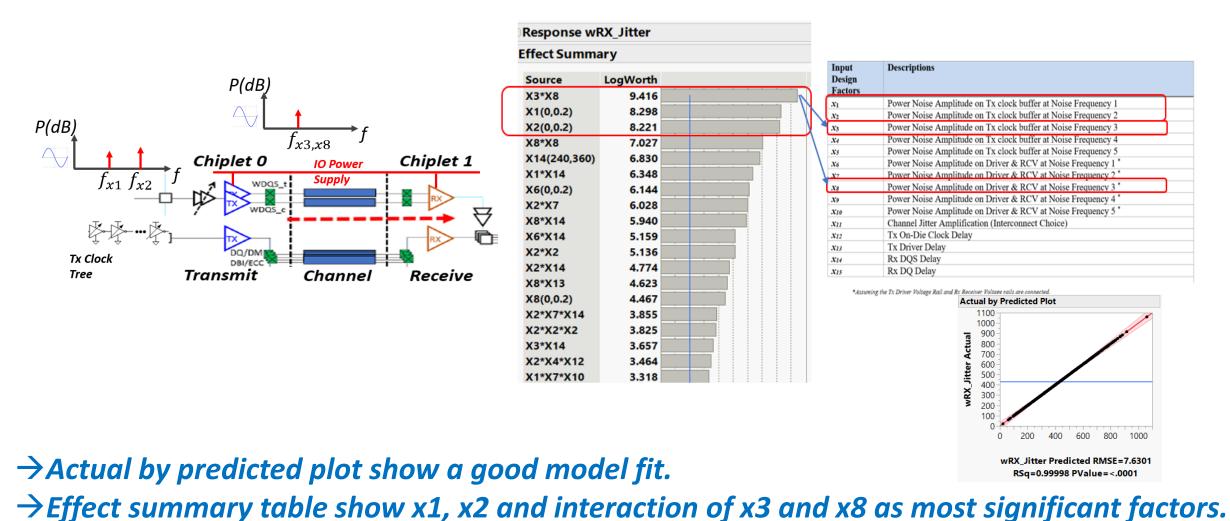

# Input Design Factor Effect Summary

© Copyright 2022 AMD

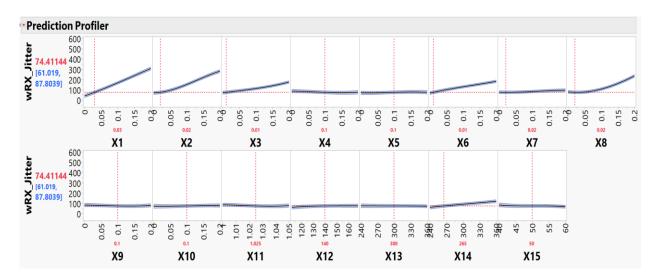

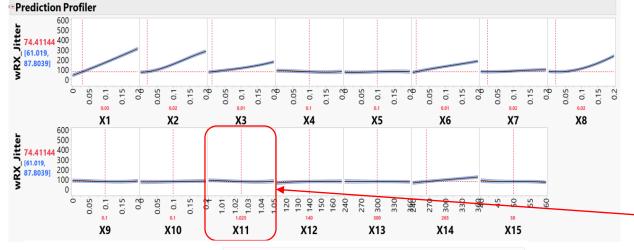

# Input Design Factor Sensitivity Read Out

| Input<br>Design<br>Factors | Descriptions                                                  |

|----------------------------|---------------------------------------------------------------|

| $x_1$                      | Power Noise Amplitude on Tx clock buffer at Noise Frequency 1 |

| $x_2$                      | Power Noise Amplitude on Tx clock buffer at Noise Frequency 2 |

| <i>x</i> <sub>3</sub>      | Power Noise Amplitude on Tx clock buffer at Noise Frequency 3 |

| X4                         | Power Noise Amplitude on Tx clock buffer at Noise Frequency 4 |

| <i>x</i> <sub>5</sub>      | Power Noise Amplitude on Tx clock buffer at Noise Frequency 5 |

| $x_6$                      | Power Noise Amplitude on Driver & RCV at Noise Frequency 1 *  |

| <b>x</b> <sub>7</sub>      | Power Noise Amplitude on Driver & RCV at Noise Frequency 2 *  |

| $x_{\delta}$               | Power Noise Amplitude on Driver & RCV at Noise Frequency 3 *  |

| X9                         | Power Noise Amplitude on Driver & RCV at Noise Frequency 4 *  |

| x <sub>10</sub>            | Power Noise Amplitude on Driver & RCV at Noise Frequency 5 *  |

| x <sub>11</sub>            | Channel Jitter Amplification (Interconnect Choice)            |

| x <sub>12</sub>            | Tx On-Die Clock Delay                                         |

| X13                        | Tx Driver Delay                                               |

| X14                        | Rx DQS Delay                                                  |

| X15                        | Rx DQ Delay                                                   |

\*Assuming the Tx Driver Voltage Rail and Rx Receiver Voltage rails are connected

- → Prediction profiler captures the impact of Input Design Factors to the Output.

- → Impactful Design factors are specified & optimized 1<sup>st</sup>.

- → The Surface plot shows the dependency of two significant design factors x1 and x2 on output jitter.

- $x_1 \rightarrow Tx$  Clock Tree Noise Tone at speed &

- $x_2 \rightarrow Tx$  Clock Tree Noise Tone at  $\frac{1}{2}$  speed.

- Background

- ASIC Development Costs and Return of Investment Trends

- Overview of Chiplet Integration as a Solution & its Challenges

- Chiplet Connection

- What are the key design factors?

- How to determine these key design factors for development design & for specification?

- Design Factors (Specification Parameters) Sensitivity Analysis

- Unified System Jitter Model for Gradient Descend Quantification.

- A Case Study: Performance Evaluation based on Input Design Factor Sensitivity Results

- Summary and Conclusions

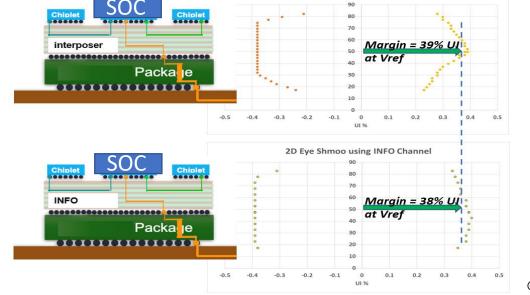

# System Jitter Shmoo Comparison between Channel Implemented by Interposer and InFO

2D Eye Shmoo using Interposer Channel

| Input<br>Design<br>Factors | Descriptions                                                  |  |  |  |

|----------------------------|---------------------------------------------------------------|--|--|--|

|                            | Davis Nais Amelitada an Tradada huffar et Nais Tradada 1      |  |  |  |

| $x_1$                      | Power Noise Amplitude on Tx clock buffer at Noise Frequency 1 |  |  |  |

| $x_2$                      | Power Noise Amplitude on Tx clock buffer at Noise Frequency 2 |  |  |  |

| $x_3$                      | Power Noise Amplitude on Tx clock buffer at Noise Frequency 3 |  |  |  |

| X4                         | Power Noise Amplitude on Tx clock buffer at Noise Frequency 4 |  |  |  |

| <b>X</b> 5                 | Power Noise Amplitude on Tx clock buffer at Noise Frequency 5 |  |  |  |

| $x_6$                      | Power Noise Amplitude on Driver & RCV at Noise Frequency 1 *  |  |  |  |

| <b>x</b> <sub>7</sub>      | Power Noise Amplitude on Driver & RCV at Noise Frequency 2 *  |  |  |  |

| $x_{\delta}$               | Power Noise Amplitude on Driver & RCV at Noise Frequency 3 *  |  |  |  |

| X9                         | Power Noise Amplitude on Driver & RCV at Noise Frequency 4 *  |  |  |  |

| X10                        | Power Noise Amplitude on Driver & RCV at Noise Frequency 5 *  |  |  |  |

| x <sub>11</sub>            | Channel Jitter Amplification (Interconnect Choice)            |  |  |  |

| x <sub>12</sub>            | Tx On-Die Clock Delay                                         |  |  |  |

| x <sub>13</sub>            | Tx Driver Delay                                               |  |  |  |

| x <sub>14</sub>            | Rx DQS Delay                                                  |  |  |  |

| <i>x</i> <sub>15</sub>     | Rx DQ Delay                                                   |  |  |  |

<sup>\*</sup>Assuming the Tx Driver Voltage Rail and Rx Receiver Voltage rails are connected

→ Sensitivity Analysis Allows a Prediction of successful channel media trade.

- Background

- ASIC Development Costs and Return of Investment Trends

- Overview of Chiplet Integration as a Solution & its Challenges

- Chiplet Connection

- What are the key design factors?

- How to determine these key design factors for development design & for specification?

- Design Factors (Specification Parameters) Sensitivity Analysis

- Unified System Jitter Model for Gradient Descend Quantification.

- A Case Study: Performance Evaluation based on Input Design Factor Sensitivity Results

- Summary and Conclusions

# **Summary & Key Takeaways**

#### •Monolithic Silicon System On Chip (SOC) Integration ROI Slow Down:-

Due to Silicon Technology scaling decelerated.

#### •Chiplet Implementation as a Solution:-

New Integration provides a new way to incorporate different features to system SOC. But.... Also create new challenges!

#### •New Challenges:-

Heterogenous integration requires identifying key design factors for specifications as well as for system optimizations.

#### •A Systematic & Holistic approach is presented based on a unified system jitter model.

Unified Jitter Model was developed to combine the input design factors effects.

The model was correlated with empirical measurement.

Unified Jitter Model was used to generate training examples and for sensitivity analysis.

#### A Case Study Application

Demonstrated the application flow which quantified the impact of changing of chiplet interconnect media.

<u>Identifying Key Design Factors for Specification Systematically is crucial for ECO</u> System Enabling.

### Thank You!!

**Q & A**

#### COPYRIGHT NOTICE

This multimedia file is copyright © 2022 by MEPTEC. All rights reserved. It may not be duplicated or distributed in any form without prior written approval.

The content of this presentation is the work and opinion of the author(s) and is reproduced here as presented at the **Road to Chiplets: Design Integration** (May 10-12, 2022).

The MEPTEC logo and 'MEPTEC' are trademarks of MEPTEC.

www.meptec.org