# Semiconductor Industry Speaker Series

"An EDA Perspective:

What's the Difference Between Heterogenous Integration and System in Package (SiP)"

John Park

Cadence Design System

March 10, 2021

www.meptec.org

www.imaps.org

An EDA Perspective: What's the Difference Between Heterogenous Integration and System in Package (SiP)

John Park

Advanced IC Packaging and Cross-Platform Solutions

### **Outline**

Overview of SiP vs Heterogenous Integration

What's Driving Heterogenous Integration Trends

Design Challenges for Heterogenous Architectures

Design Flows for Next-Gen Packaging

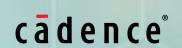

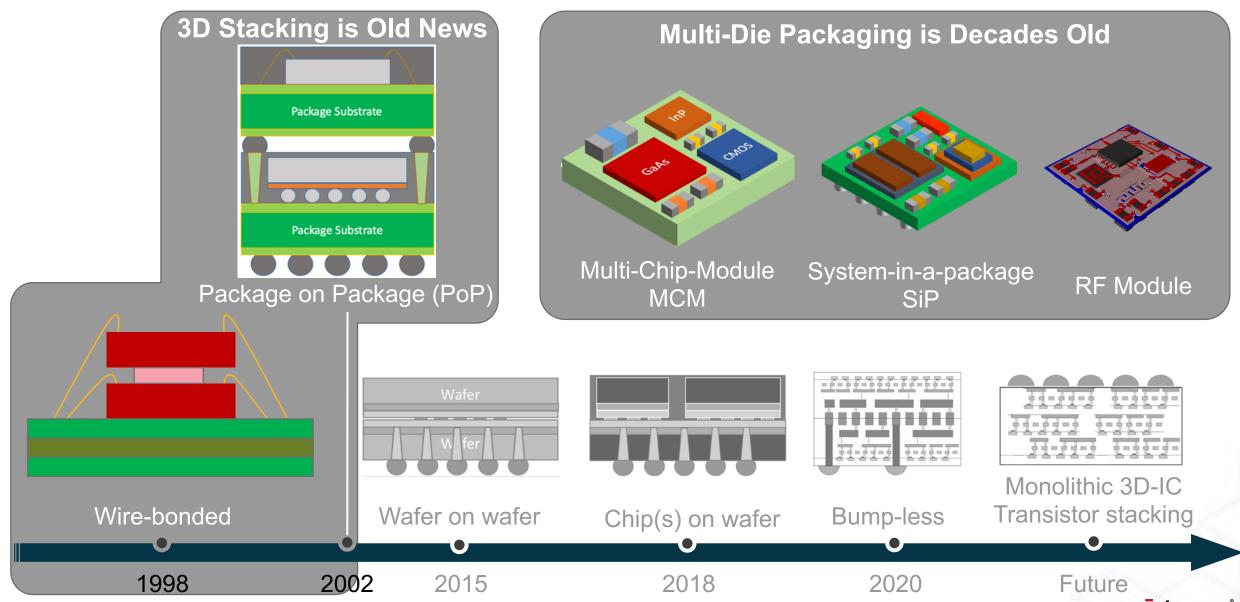

### Evolution of Advanced Multi-Chip(let) Packaging Technologies

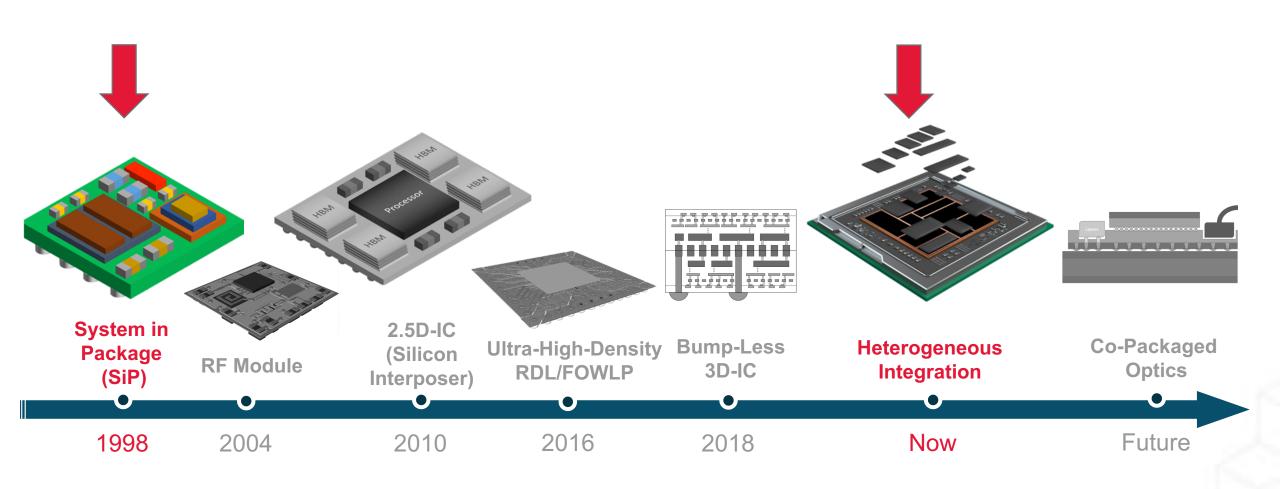

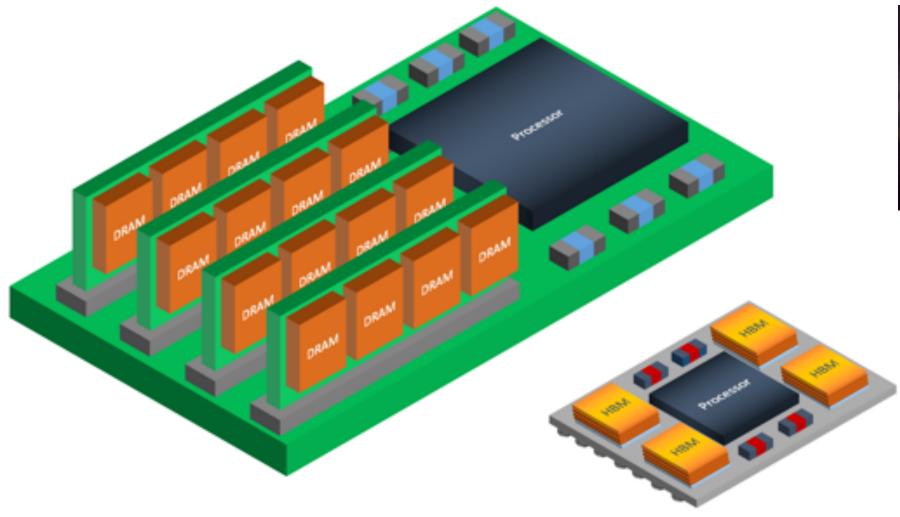

## SiP/MCM vs. Chiplet-Based (Heterogeneous Integration) Architectures

New: The transition from system on a chip (SoC) to system in a package (SiP)

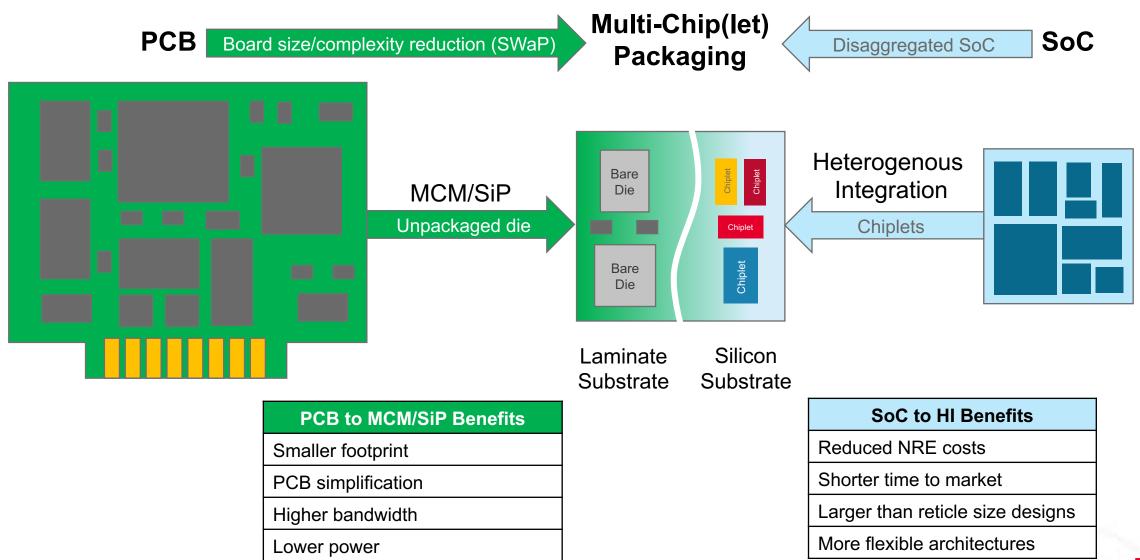

# Heterogenous Integration is Just a Different Way of Logically Partitioning an SoC and is Independent of Packaging Technology

Leveraging SiP design-style approach becoming a viable alternative to monolithic SoC

Modular approach vs monolithic approach

Not every logic function (IP) needs to be designed in the same process node (heterogeneous integration)

- Leveraging IP in the form of chiplets

- IP that is physically realized working on a standard communication interface

- Similar to board-level design

- Multiple options are available for "packaging" chiplets

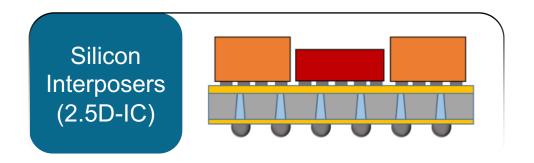

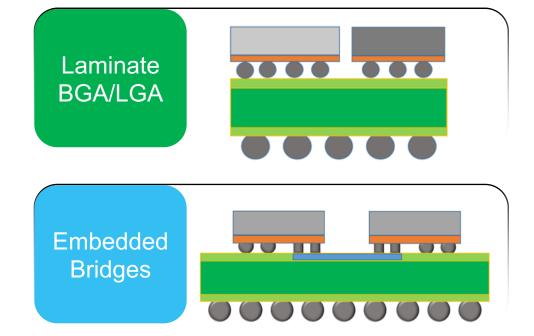

- Includes latest IC packaging 2.5D/3D-IC, FOWLP and embedded bridges

#### Hard IP

GDSII layout Tied to specific technology/node

#### Soft IP

Synthesizable RTL Gate-level netlist Can be targeted to specific technology/node Physically realized and tested (hardened) IP wrapped with micro-buffers driving standard communication interface, level-shifting, etc

### SiP vs. Heterogenous Integration

| System in a Package (SiP)                        |                                         |                                        |  |

|--------------------------------------------------|-----------------------------------------|----------------------------------------|--|

| Simplify/shrink<br>PCB                           | Higher performance, smaller form-factor | Much lower cost than transition to SoC |  |

| Schematic-driven PCB-like design flow            | Little/no STA                           | Min/max/matched routing lengths        |  |

| Moves devices closer together (unpackaged chips) | Shorter signal paths, less power        | Bigger thermal challenge               |  |

|                                                  | Flip-chip attach                        | 100um-180um                            |  |

|                                                  | Bond-wire attach                        | Can be stacked                         |  |

| Integration fabric                               | Laminate/organic substrates             | Ceramic (LTCC)                         |  |

| Heterogenous Integration                       |                                                       |                                                                      |

|------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------|

| Modularized/Disa ggregate SoC                  | Reduced cost<br>(relative to<br>advanced node<br>SoC) | Design/architectur<br>e flexibility and<br>reduced time to<br>market |

| Text/language<br>driven IC-like<br>design flow | Still requires<br>formal IC-like<br>sign-off process  | Min/max/match interconnect to meet timing                            |

| Devices father apart (multiple chiplets)       | Longer signal paths, more IO, larger form-factor      | Bigger thermal challenge when 3D stacking                            |

|                                                | Every chiplet is flip-chip-like attach                | 55um and smaller pitch                                               |

| Targeted integration fabric                    | Silicon                                               | Also, glass,<br>embedded<br>bridges & FOWLP                          |

Why would we want to do this? What happened to PPA?

### Outline

Overview of SiP vs Heterogenous Integration

What's Driving Heterogenous Integration Trends

Design Challenges for Heterogenous Architectures

Design Flows for Next-Gen Packaging

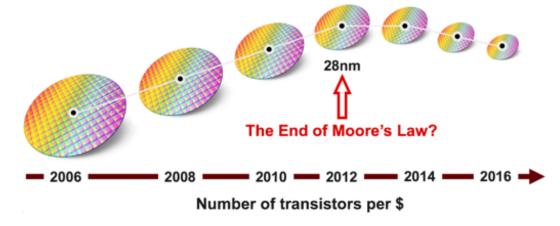

# The End of Moore's Law & The Beginning of "More-Than-Moore"

For the past five decades, the electronic industry has thrived while enjoying the benefits of Moore's Law. But things are changing...The economics of semiconductor logic scaling are gone...

Gordon Moore knew this day would come. He also predicted that "It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected."

Providing a possible alternative to advanced monolithic SoCs, multi-chiplet SiPs have become a very attractive option for cost-sensitive complex designs

The generation of "More Than Moore" is here...

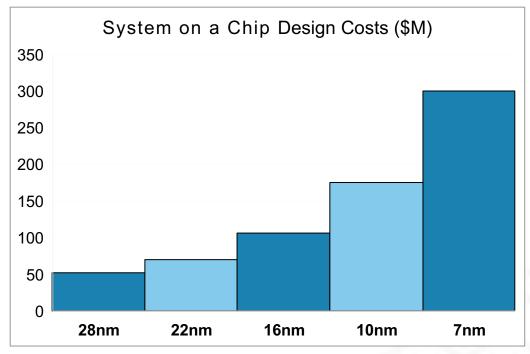

### The End of Moore's Law...Really?

- It's more than the limitations of physics...

- Cost per transistor has steadily increased since 2012/3 (28nm)

- Designing IC's at the latest nodes is hard and expensive

- Low-volume businesses can't justify the NRE costs of designing an SoC at the latest node

- Requires huge teams of engineering specialists that aren't always easy to find

- Systems and software companies now designing chips and challenging the status-quo of SoC approach

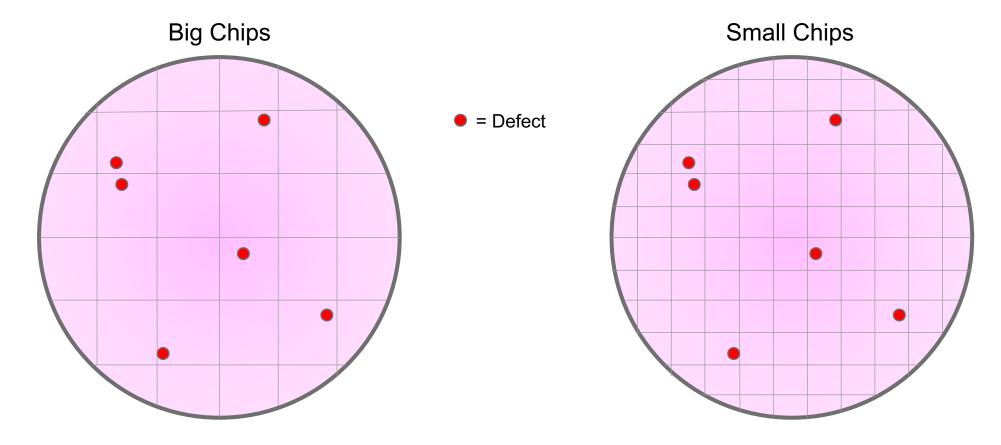

- Today's SoCs are reaching reticle limits...but big chips typically don't yield anyways\*

- More analog/RF content in today's designs

- Analog/RF never have benefited from transistor scaling

- Cost of Analog IP recertification at every node probably doesn't make sense in many cases

### Why Large Die Don't Yield?

- Same size wafer, same number of defects:

- The wafer on the left produces 10 working chips (62% yield)

- The wafer on the right produces 72 working chip(let)s (92% yield)

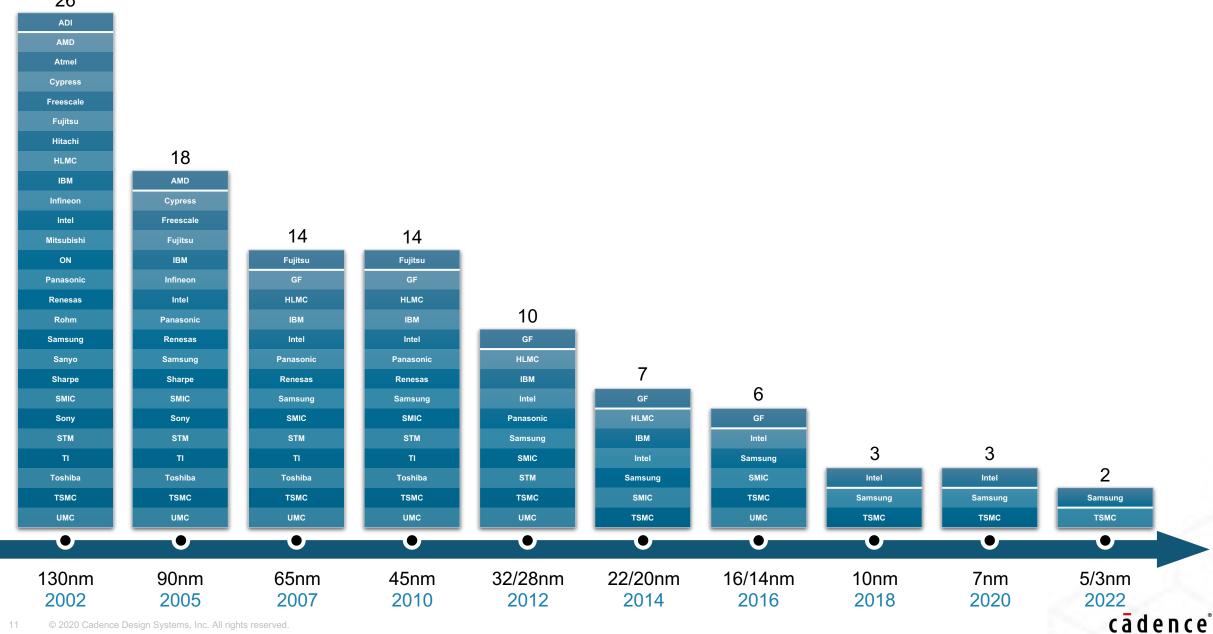

### Getting Your Chip Built, The Options Are Diminishing

### The World of IC Design Turns To Packaging...

## Final Hurdles for Chiplets to Move into Mainstream

Commercialization/standardization of chiplets

- Today most chiplet-based designs are single vendor

- Closed ecosystem

- The next step forward will likely require commercialization of chiplets

- Standards and business model needed before IP companies proceed

- Ongoing work to define standards for chiplet-to-chiplet communication interface and data-exchange formats

- Must be low power, low BER and low latency…

No single PHY can do it all

- Open Compute Project (OCP) and USG programsBoW, OpenHBI, XSR, AIB, ...

- What about Analog/RF?

- What about test/KGD? Who "owns" design yield?

- Who manages chiplet inventory. Board part providers?

- Will compromised PPA be acceptable for all applications?

| Interface Considerations<br>Serial, Parallel or Proprietary |  |

|-------------------------------------------------------------|--|

| Package type                                                |  |

| Reach                                                       |  |

| Power (pJ/bit)                                              |  |

| Latency                                                     |  |

| Speed                                                       |  |

| Bandwidth                                                   |  |

| Routing complexity                                          |  |

| Test, ESD, ???                                              |  |

| Monolithic SoC | Chiplet-Based |  |

|----------------|---------------|--|

| High           |               |  |

| High           |               |  |

| High           |               |  |

|                | Acceptable?   |  |

|                | Acceptable?   |  |

|                | Acceptable?   |  |

|                | High<br>High  |  |

### Outline

Overview of SiP vs Heterogenous Integration

What's Driving Heterogenous Integration Trends

Design Challenges for Heterogenous Architectures

Design Flows for Next-Gen Packaging

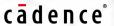

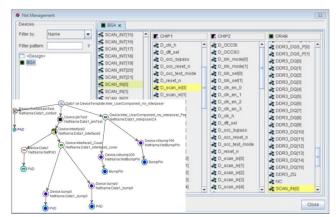

### Bottom Line...Design and Verification is Only Getting Harder

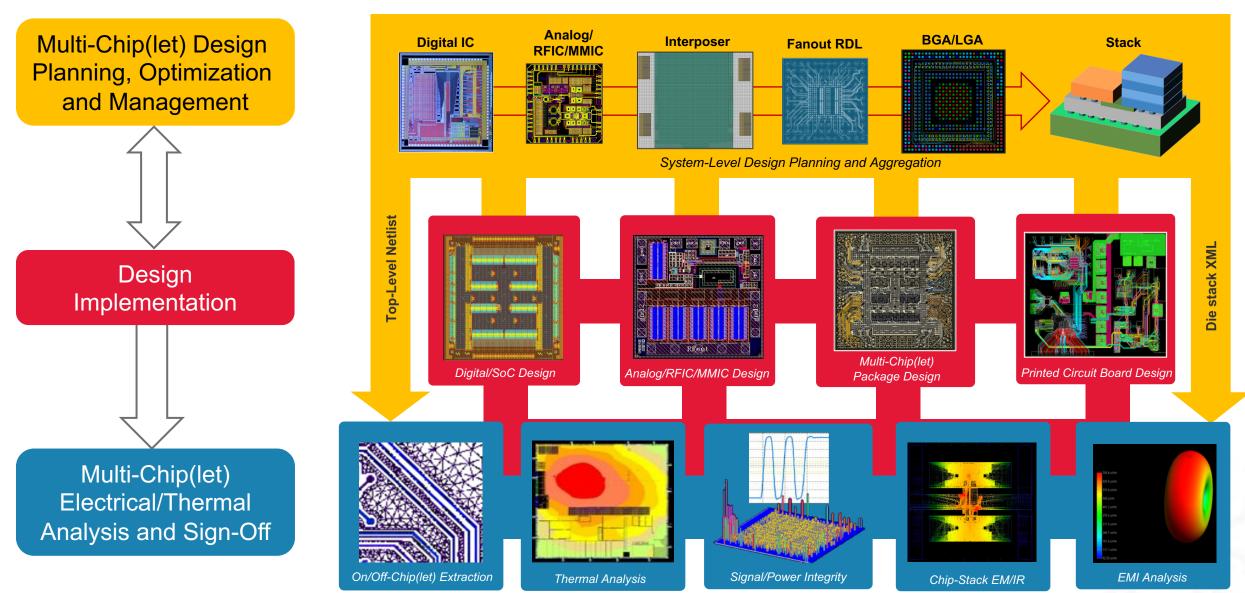

## Design Tool/Flow Challenges for The Entire Layout Chain

- Requires design tools and flows that support crossfunctional collaboration (co-design) for all design teams

- Complete system-level visualization in a single tool

- With the ability to optimize the system-level design and crossdomain interconnect

- Pin-out and floorplan (including stack) optimization

- Signal name aliasing across domains

- Direct read/write into multiple layout domains and tools

- Editing environment with userspecific design orientation

- Cross-domain ECO loop

- Domain-specific editing controls

- Accept/Reject changes

# Design Tool/Flow Challenges for the Ecosystem

Assembly Design Kits (ADK) Looking Beyond Design-Rule Manuals and Reference Designs...

#### TechFiles

Layer stack-up

Material

**Properties**

**Thickness**

Physical/Electrical layout constraints

#### Design Libraries

#### **Footprints**

Discrete

BGA/LGA

3D Mechanical

Bond-Wire profiles

IO models

Thermal models

Power models

#### Assembly Rules

Device placement constraints based on assembly pick & place equipment

Die to die spacing

Device to device

Device to obstacle

#### Compliance Kits

Electrical spec validation of chip(let)-to-chip(let) interfaces\*

Jitter tolerance

Insertion loss

Return loss

Eye mask

#### Manufacturing Rules

# Board/substrate manufacturing process

Substrate checks

Soldermask checks

Soldering issues

Silkscreen checks

#### Rule Decks

Foundry/semiconductor manufacturing process

DRC

LVS

Metal fill

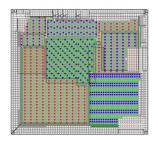

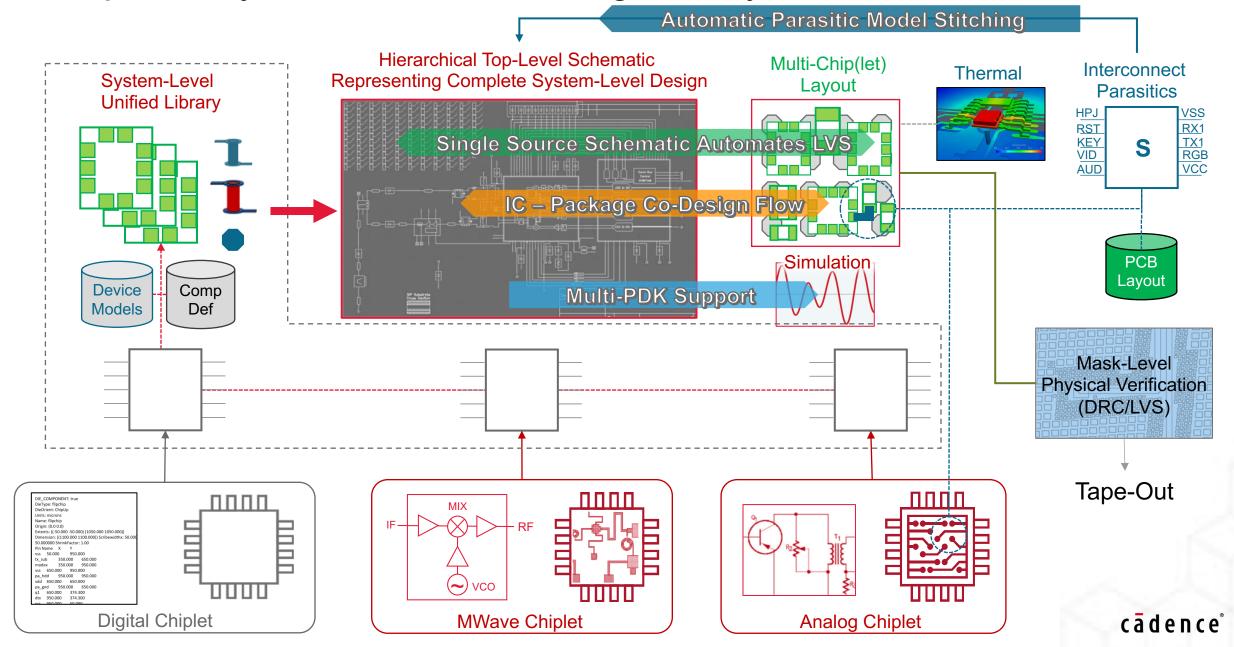

## Design Tool/Flow Challenges for the Package Design Team

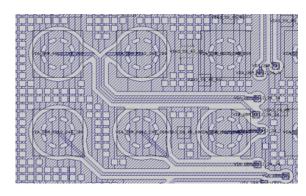

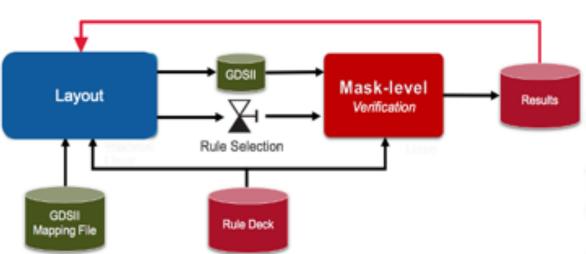

Advanced multi-chip(let) silicon-based packages require specialized layout features and formal physical/logical verification capabilities

- Layout features specific to silicon substrate designs

- Advanced filleting and trace widening

- Progressive shape and pad degassing algorithms

- High-capacity design support

- Mask-level accurate output data (GDSII) from substrate layout tool

- Advanced arc vectorization

- Seamless integration with IC physical verification tool with feedback loop to layout

- 1. Mask-level DRC

- 2. Connectivity verification (LVS) of multi-chip(let) designs

- 3. Region specific advanced metal fill (balancing)

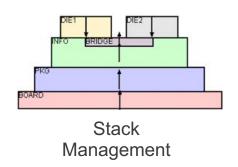

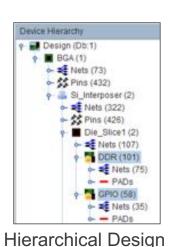

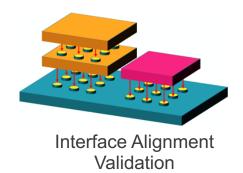

### Design Tool/Flow Challenges for the IC Design Architect

- Top-level design aggregation, management and system-level optimization

- Integrated with sign-off tools for stack alignment and layout vs schematic (LVS) checking

Advanced Bump/TSV Planning

Hierarchical Signal Mapping

System-Level Connectivity Optimization

Management

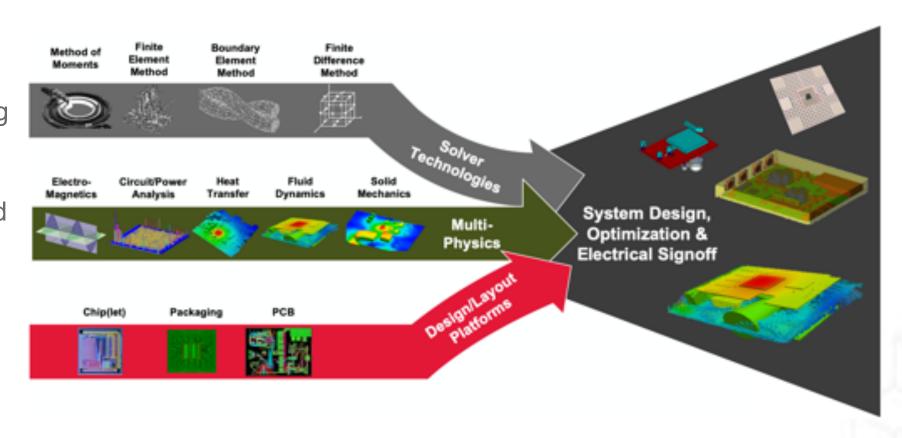

### Design Tool/Flow Challenges for Electrical/Thermal Analysis

- Analysis at the system level requires multiple simulation solutions

- On-chip and off-chip EM modeling and analysis

- Device, interconnect and antenna

- Layout conditioning

- Chip/package/board cross-domain coupling

- Back-annotation to top-level design

- In-design analysis and electrical sign-off verification

- Thermal coupled with power analysis

- Thermal self-heating coupled with CFD

- Seamless integration with layout tools

### Outline

Overview of SiP vs Heterogenous Integration

What's Driving Heterogenous Integration Trends

Design Challenges for Heterogenous Architectures

Design Flows for Next-Gen Packaging

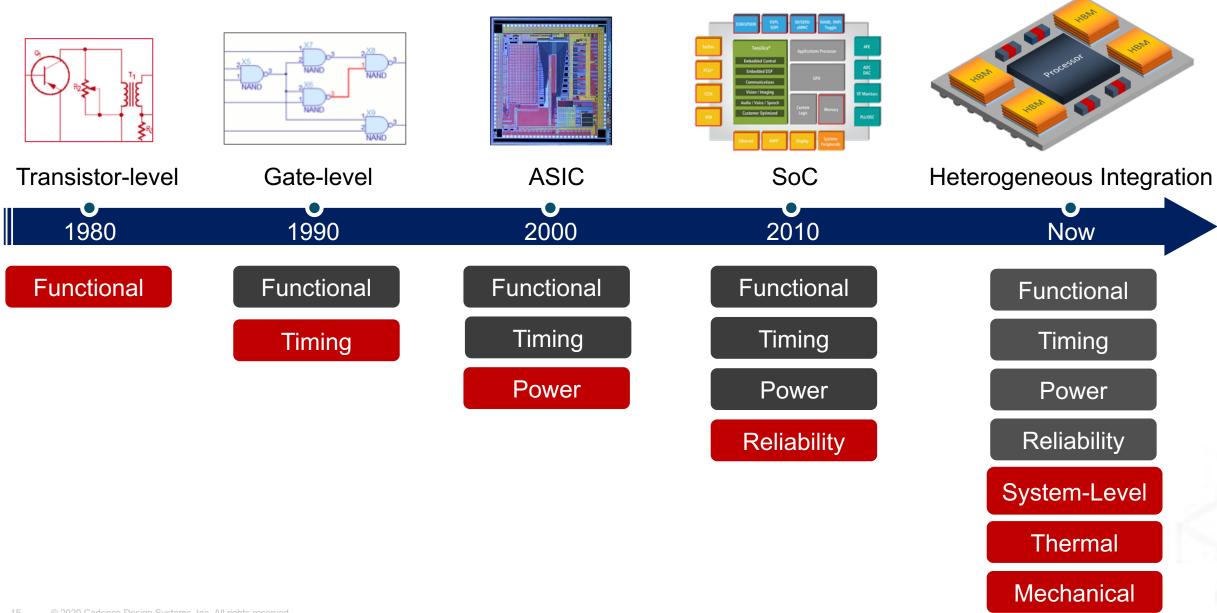

### Transitioning to System-Level Design/Analysis Tools/Flows

## Example of System-Level Co-Design/Analysis Flow for HI

# Question: What Is This?

### It's Certainly "More Than Moore". But is it Heterogenous Integration?

### Conclusion

We have entered the More-than-More era and electronic design will get harder

SiP technologies being leveraged by IC designers to create heterogeneously integrated architectures

New challenges face package designers and IC designers

New design tools and flows will be required

# cādence®

© 2020 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="www.cadence.com/go/trademarks">www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or cadence Design Systems, Inc. Accellera and SystemC are trademarks of Accellera Systems Initiative Inc. All Arm products are registered trademarks or trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All MIPI specifications are registered trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks are the property of their respective owners.

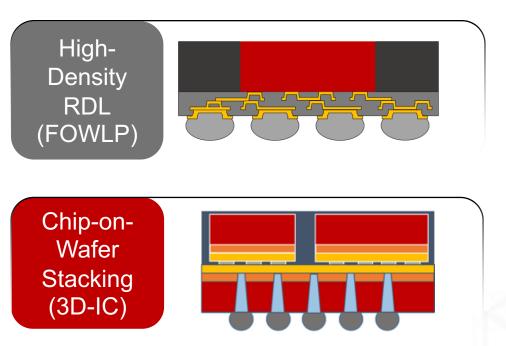

## Packaging Technologies Being Targeted for Heterogenous Integration

# **COPYRIGHT NOTICE**

The presentation in this publication was presented at the MEPTEC—IMAPS Semiconductor Industry Speaker Series. The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC, IMAPS, or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.