# Road to Chiplets: Architecture July 13 & 14, 2021

## Chiplet Architectural Considerations for Adoption and Scaling

Rob Munoz, Principal Engineer, Design and Engineering Group

With numerous contributions from Intel's Chiplet Work Group (special thanks to Dave Kehlet, Tanay Karnik, Ramune Nagisetty, Peter Onufryk, and others)

July 14, 2021

## Legal Information

© INTEL CORPORATION. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries.

\*Other names and brands may be claimed as the property of others.

LEGAL DISCLAIMER: Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com. Software and workloads used in performance tests may be optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information, visit www.intel.com/benchmarks. Results have been estimated based on internal Intel analysis and are provided for informational purposes only. Any difference in system hardware or software design or configuration may affect actual performance. Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction. Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors.

Statements in this document that refer to future plans or expectations are forward-looking statements. These statements are based on current expectations and involve many risks and uncertainties that could cause actual results to differ materially from those expressed or implied in such statements. For more information on the factors that could cause actual results to differ materially, see our most recent earnings release and SEC filings at www.intc.com.

This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.

Intel estimated results are based on product specifications.

## Moore's Predicted "Day of Reckoning"

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected<sup>1</sup>."

-Gordon E. Moore

Image: Intel

<sup>1: &</sup>quot;Cramming more components onto integrated circuits", Electronics, Volume 38, Number 8, April 19, 1965

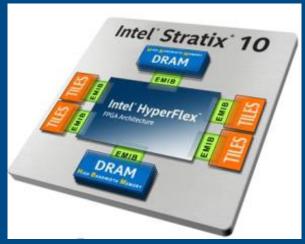

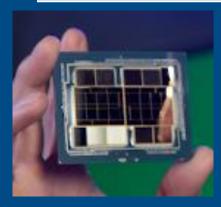

## Some Intel Products Using Chiplets

#### FPGAs

Ponte Vecchio GPU

Lakefield Client CPU

Growing Usage Across Multiple Product Families

## Chiplet Approach Value Proposition

- Lower portfolio costs

- Product cost (bigger chips with higher yields, less wasted silicon, better align delivered IP to optimal manufacturing process and related heterogeneous integration benefits, etc.)

- Project costs (more configurations with fewer die developments, internal and external reuse with easier customization, reduced IP porting expenses, etc.)

- Scale innovation and delivery capabilities

- Granular leverage of die and process-locked IP from internal and external sources

- Granular leverage of manufacturing capabilities and capacity

- Access 3D stacking benefits (XY area reduction, placing memory closer to logic)

- Reduce time to solution

- Reuse, reduce process availability/maturity and IP porting schedule and ramp risks

## Chiplet Approach Known Trade-Offs

- Tiling overheads

- Incremental area/power/performance overhead for die-to-die interface

- Incremental package, assembly, and test costs/duration and tolerance requirements, impacting throughput/time, inventory management, etc.

- Impractical to co-package multiple "hot" die or die that each need a large amount of external PCB connectivity

- Margin stacking and inventory carrying costs when using external die

- Not optimal in cases where a single "sweet spot" configuration monolithic alternative is feasible and attractive

- Die built for a 3D stack difficult to reuse and may have additional thermal challenges

## Adoption and Scaling Prerequisites

- Chiplet Based Product Volume Attach Points

- Fully Specified Interface Standards for Interoperability

- Chiplet-based Product Development and Integration Enabling IP,

Software, and Tools/Flows/Methods

- Broad Market Manufacturing, Packaging, Assembly, and Test Capabilities

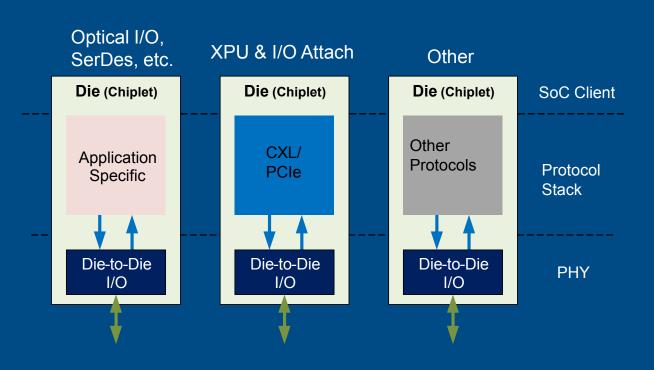

#### Die-to-Die Protocols and Use Cases

- Layer 1-Only Usage

- Ideal for SerDes, Optical I/O, etc. PHY attach

- CXL/PCle for XPU and I/O Attach

- Addresses SoC construction and interfacing issues by leveraging proven CXL/PCIe model

- CXL addresses common use cases

- PCle use cases are supported with CXL.io

- Memory use cases are supported with CXL.mem

- Accelerator use cases are supported with CXL.cache

- Other

- Other protocols (e.g. AXI et. al.) and usages

Volume Opportunity: XPU & I/O Attach

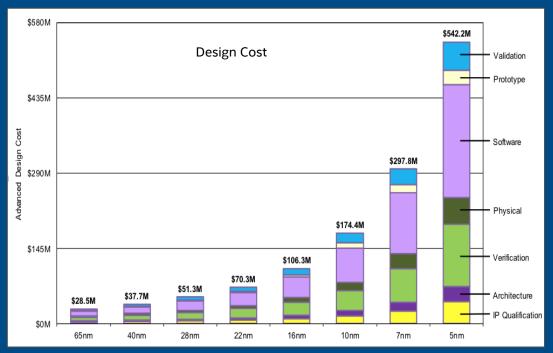

## Reuse is Key to Portfolio Cost Economics

Fewer chip design-in opportunities will individually be large enough to amortize rapidly rising leading edge chip costs

Source: IBS (as cited in IEEE Heterogeneous Integration Roadmap)

Must reuse IP/die within and between chips to manage cost mismatch

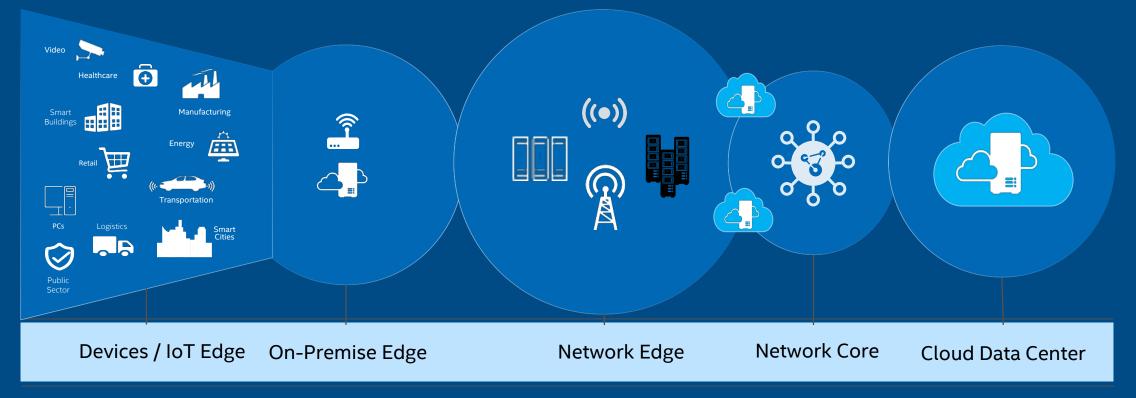

## Reuse Key to Uniform Edge to Cloud Experience

- Compute, acceleration, and I/O capabilities rightsized for deployment environment

- Common software model largely agnostic to deployment details

### Need Architected, Fully Specified Interfaces

#### Mechanical

- Bump and wire sizes

- Bonding footprint

- xyz constraints

#### Thermal

Thermal/temperature characteristics and constraints

#### **Electrical**

- Power delivery

- Noise margin

- Capacitance

#### **Functional**

- Data/transaction specifications

- Mgmt: power, security, debug, etc.

- Configuration & statistics

- Manufacturing test access

Which support

Generational Compatibility

All enabled by off-the-shelf Tools/Flows/Methods and HW/SW Building Blocks

... to support industry scale systematic reuse

## Physical Connectivity Building Blocks

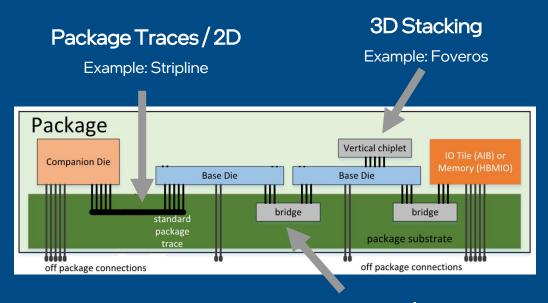

#### **Packaging Technology**

#### I/O Technology

|               | Simple I/O, Many Wires    | Complex I/O, Few Wires |

|---------------|---------------------------|------------------------|

| Advantages    | Bump Pitch Scaling        | Flexible Die Placement |

|               | Low Power                 | Std package shoreline  |

|               | Low Latency               |                        |

|               |                           |                        |

| Disadvantages | Die Placement Constraints | Higher Power           |

|               |                           | Higher Latency         |

|               |                           |                        |

| Examples      | Intel AIB and MDI         | Intel On Package I/O   |

|               | HBM Memory                | USR/XSR SerDes         |

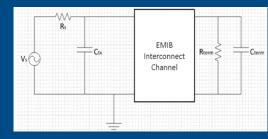

Bridge/2.xD

Example: EMIB

Many wire I/O approach best for unlocking full potential of package-level integration

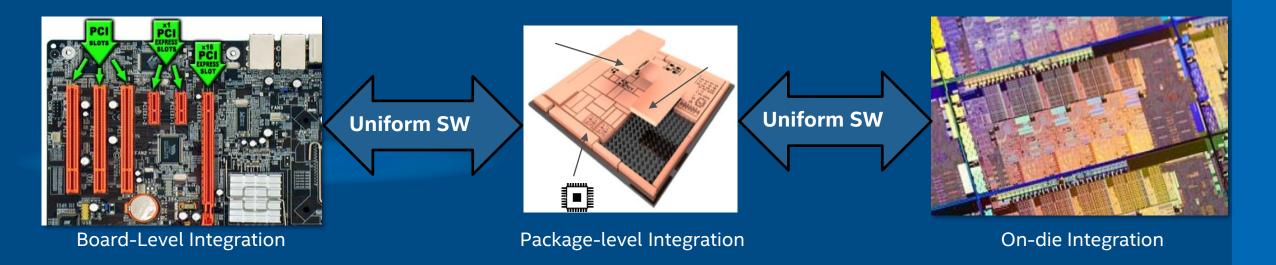

### Physical Integration-Independent IP + Software Model

- Ideally IP and associated application software are agnostic to scaling and physical integration approach

- Enables rightsizing functionality for a wide variety of target deployment environments with high reuse of IP, system, and software investments

## Summary

- Chiplet approach has tremendous potential to reshape how companies can collaborate to build many classes of chips in the future

- However, there are key adoption and scaling prerequisites that must first be met

- Layer 1 I/O attach and XPU + I/O attach are important early use cases to address

- Using CXL/PCIe to support XPU + I/O attach usages enables more rapid adoption, providing ecosystem carryover with a uniform software model

#

## Thank you sponsors!

## ADVANTEST®

SYNOPSYS®

#### Global Companies Rate Advantest THE BEST ATE Company 2021

Advantest receives highest ratings from customers in annual VLSIresearch Customer Satisfaction Survey for 2 consecutive years.

Global customers name Advantest THE BEST supplier of test equipment in 2020 and 2021, with highest ratings in categories of:

Technical Leadership - Partnership - Trust - Recommended Supplier - Field Service

"Year-after-year the company has delivered on its promise of technological excellence and it remains clear that Advantest keeps their customers' successes central to their strategy. Congratulations on celebrating 33 years of recognition for outstanding customer satisfaction."

— Risto Puhakka, President VLSIresearch

## Amkor's Differentiators

#### Technology

Advanced Packaging Leadership Engineering Services Broad Portfolio

#### Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

# SYNOPSYS®

Silicon to Software™

#### **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Architecture Workshop** (July 13 & 14, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org