# Road to Chiplets: Architecture July 13 & 14, 2021

# Why Chiplets?

TRACK INNOVATION

IDENTIFY TRENDS

ANALYZE GROWTH

INFLUENCE DECISIONS

E. Jan Vardaman, President and Founder

RELEVANT, ACCURATE, TIMELY

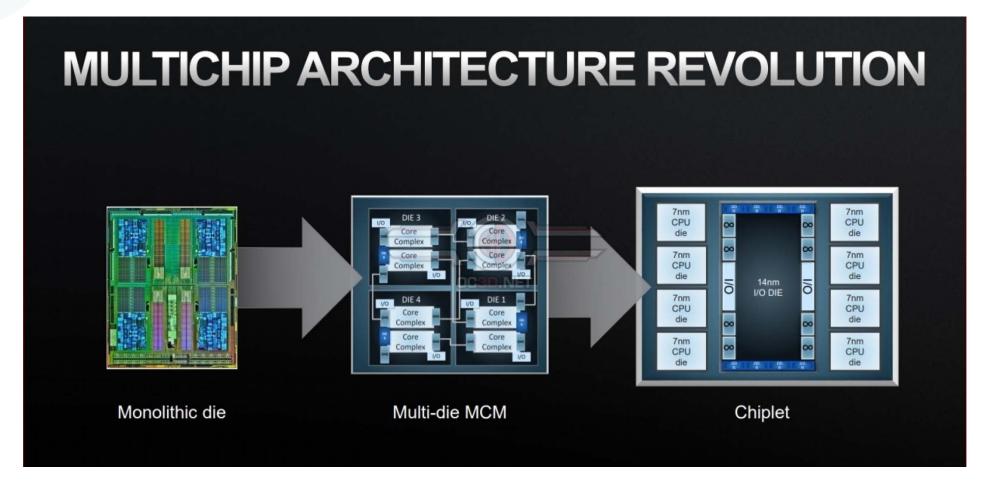

#### **New Era of Semiconductor Packaging**

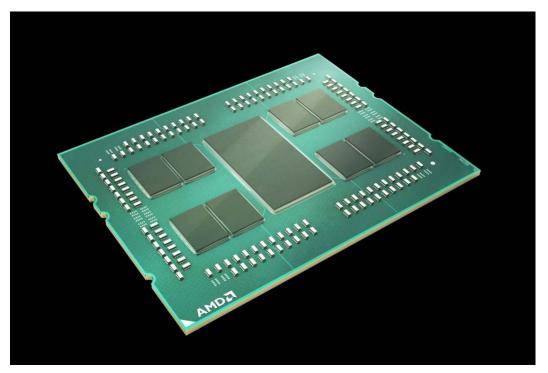

Source: Overclock3d.net.

Chiplets will be a key enabler for next 10-20 years (to quote from TSMC's Doug Yu)

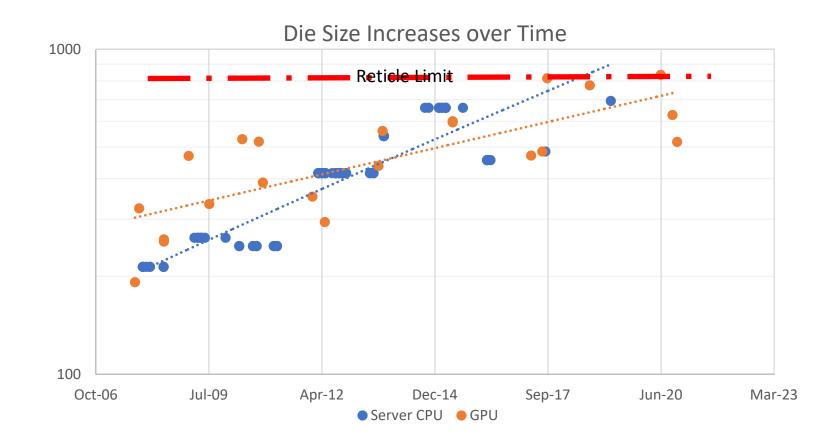

### Die Size Growth: Major Driver for Adoption of Chiplets

Die sizes continued to increase over time for server CPU and GPU

Performance requires more transistors, but industry needs a new, more economical approach

Source: AMD internal analysis.

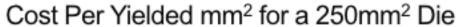

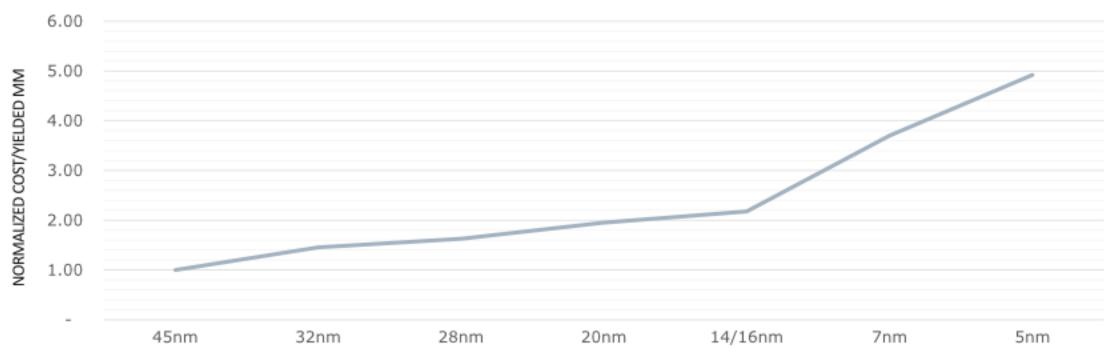

#### **Cost of Fabricating a Large Die Continues to Increase**

Source: AMD internal analysis.

- As companies move into <7nm semiconductor nodes, the cost to fabricated a large die becomes uneconomical

- The industry needs a new approach to achieve the economics previously achieved with scaling

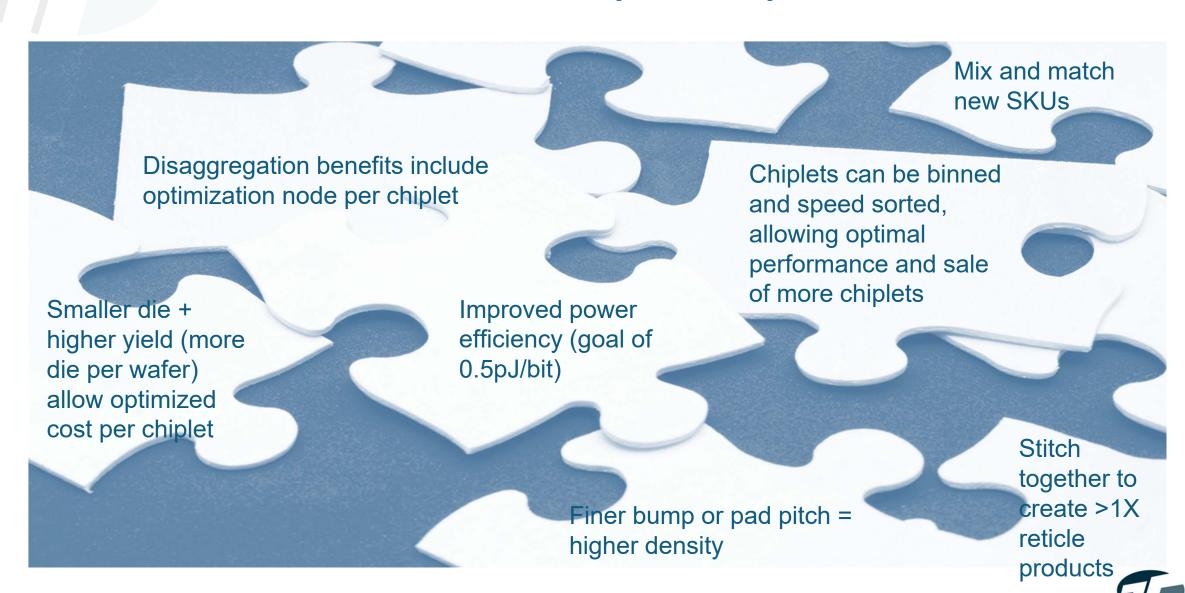

#### **Drivers for Chiplet Adoption**

#### **How Do We Define Chiplets?**

- A chiplet is an integrated circuit block specifically designed to work with other chiplets to form a larger more complex system that often makes use of reusable IP blocks

- A chiplet can be created by partitioning a die into functions that are more cost effectively fabricated (smaller die, higher yield, and less advanced nodes)

- A chiplet is a hard IP block

- Functions with other chiplets, so design must be co-optimized and silicon cannot be designed in isolation

- Made possible by communication using chiplet interface (proprietary today)

- Differs from SiP or traditional MCM in that it is a new design, not just a combination of different "off-the-shelf" chips

- Chiplet is not the package, it's the design philosophy

- Change from "silicon centric thinking" to "system-level planning" and "co-design of IC and package"

- The industry has to think about chip design in a new way

- Same impact as when the industry moved from a peripheral chip layout to area array!

### What is A Chiplet Package?

#### Many package options "no one size fits all"

- Organic substrate, including an embedded bridge

- Silicon interposer

- Fan-out on Substrate or RDL interposer

- 3D configurations with µbumps or hybrid direct bonding

Source: Wired.com.

Source: Xilinx.

Source: TechSearch International, Inc. teardown.

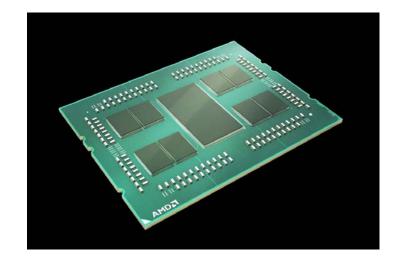

#### **AMD Multiple Chiplet Product Introductions**

- Multiple generations of desktop and server products using chiplets with organic substrate

- Split out analog functions from advanced 7nm logic

- Chiplets can be binned and speedsorted before assembly on the substrate

- Better memory access

- Minimize local latency

- 1, 2, 4 or 8 CPU chiplets plus an I/O chiplet are attached to an organic interposer

Source: Wired.com.

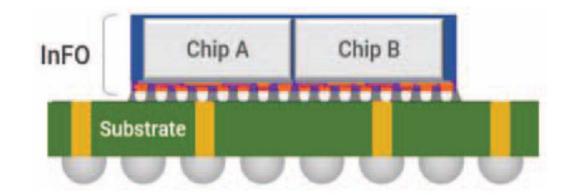

### TSMC InFO\_oS for Chiplets

- TSMC has proposed the use of its InFO process as a chiplet packaging solution targeted at Al, networking, & edge computing

- Alternative to the laminate

MCM package for chiplets

- Demonstration of 2.5x reticle of fan-out (51mm x 42mm) on a 110mm x 110mm substrate

- 5 RDLs (4 with 2/2μm 1 with 5/5 μm)

- D2D I/O pitch 36 μm

| Technology     | MCM         | InFO_oS     |  |

|----------------|-------------|-------------|--|

| Structure      | Chip1 Chip2 | Chip1 Chip2 |  |

| Min. Line W/S  | 15/15 um    | 2/2 um      |  |

| Line counts/mm | 34          | 250         |  |

| BW/mm          | 1x          | 7.3x        |  |

Source: TSMC.

## Fan-Out and/or Embedded Bridge Solutions for Chiplets

- Many companies with embedded bridge solutions or FO solutions

- Amkor

- ASE

- IBM

- Intel

- SPIL

- TSMC

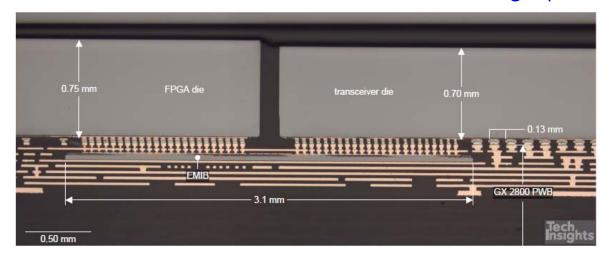

#### Intel's Embedded Multi-die Interconnect Bridge (EMIB)

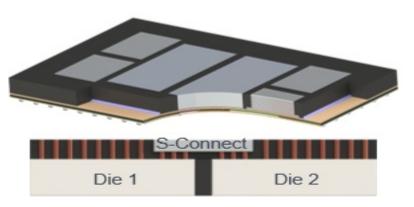

S-Connect

Source: Amkor Technology

Source: ASE.

Source: TechInsights.

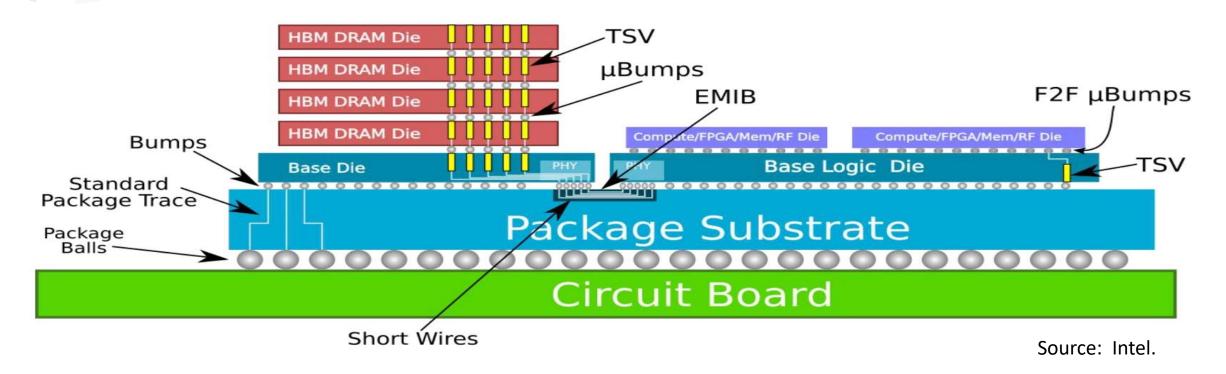

### **Intel Foveros Technology**

#### Intel's Foveros technology die are stacked in 3D

Base die, using less advanced node, can include power management features, voltage regulators, DC/DC converters

#### Benefits include

- Reduced voltage drop

- Power efficiency

- More immediate power delivery to the CPU cores

- Elimination of passives on substrate

- System-wide communication across multiple chiplets/dice vs. the limited die-to-die communication capability enabled by passive Si interposers

#### Used in the Samsung Galaxy Note S (Mobile PC)

- Longer lasting battery

- No fan

- Very thin package, allows thin product

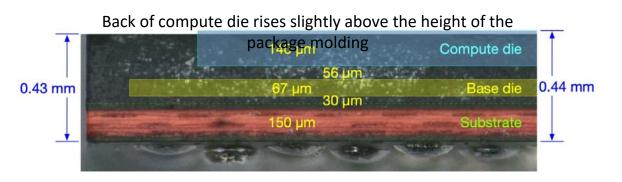

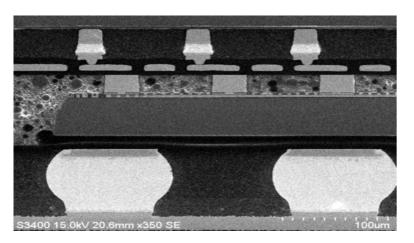

#### **Intel's Lakefield CPU**

- 10nm CPU

- 22nm Active Si Interposer

Source: Intel.

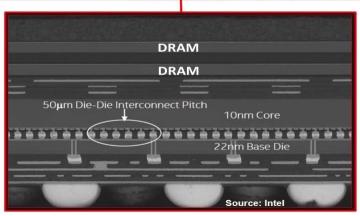

#### Intel Co-EMIB (EMIB + Foveros)

- EMIB and Foveros can be combined to provide a high-density solution

- Connecting HBM and logic with silicon bridge embedded in laminate substrate

- Foveros used to connect chiplets (Intel calls tiles)

- Will be used for Intel's upcoming datacenter GPU

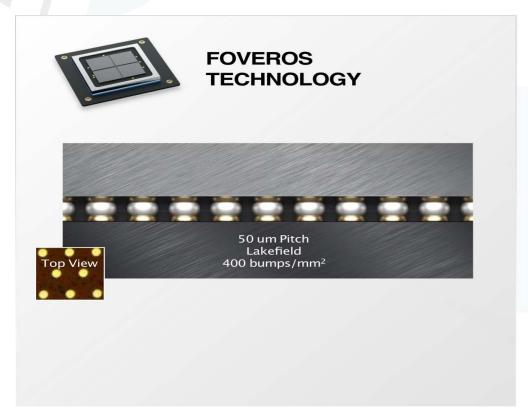

#### **Hybrid Bonding**

**FUTURE** Area scales with bump pitch 10 um Pitch **Hybrid Bonding** Top View 10000 bumps/mm2 Smaller, simpler circuits Lower capacitance Lower power

Source: Intel.

- No solder interconnect

- Finer pad pitch joining is possible

- Requires clean surface (no particles), clean environment

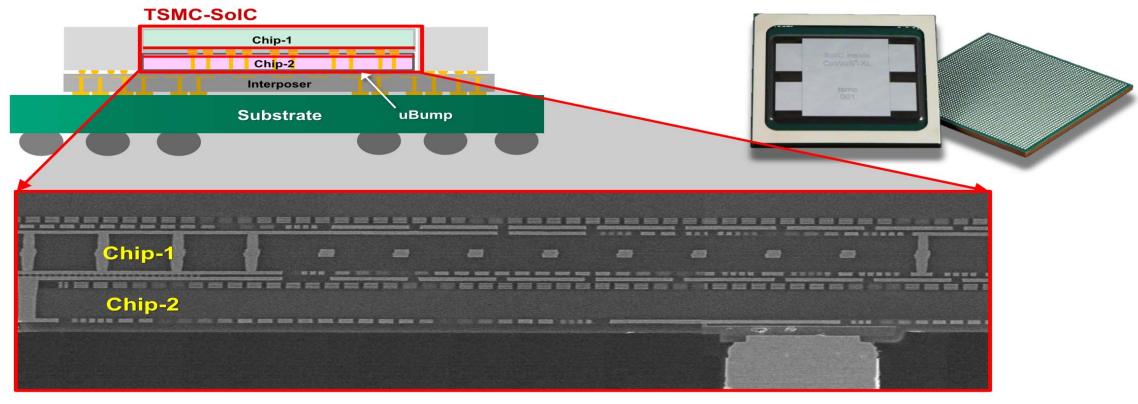

# **TSMC-SolC**<sup>™</sup> + CoWoS<sup>®</sup> for HPC Applications

Source: TSMC.

- SoIC can be attached to a silicon interposer

- SoIC can be used to stack 4, 8, or 12 high chips with a total height of 600 μm

#### **SolC™** Compared to 2.5D and 3D IC

| Technology                       | 2.5D                                      | 3D-IC                | SolC                |

|----------------------------------|-------------------------------------------|----------------------|---------------------|

| Structure<br>cross-section       | SoC1 SoC2    SoC2     BEOL     Interposer | SoC1 8 Fubump 8 SoC2 | SoC1 SolC Bond SoC2 |

| Interconnect                     | µbump + BEOL                              | μbump                | SoIC bond           |

| Chip Distance                    | ~100 µm                                   | ~30 µm               | 0                   |

| Bond-pad Pitch                   | 36µm (1.0X)                               | 36μm (1.0X)          | 9μm (0.25X)         |

| Speed                            | 0.01X                                     | 1.0X                 | 11.9X               |

| Bandwidth Density                | 0.01X                                     | 1.0X                 | 191.0X              |

| Power Efficiency<br>(Energy/bit) | 22.9X                                     | 1.0X                 | 0.05X               |

Source: TSMC.

- With SoIC there is virtually no distance between integrated chips, and a very small bond-pad pitch of 9  $\mu$ m provides good scalability

- Using a bumpless bonding process is critical to improvements in performance, power, resistance, and capacitance (lower inductance and thermal resistance)

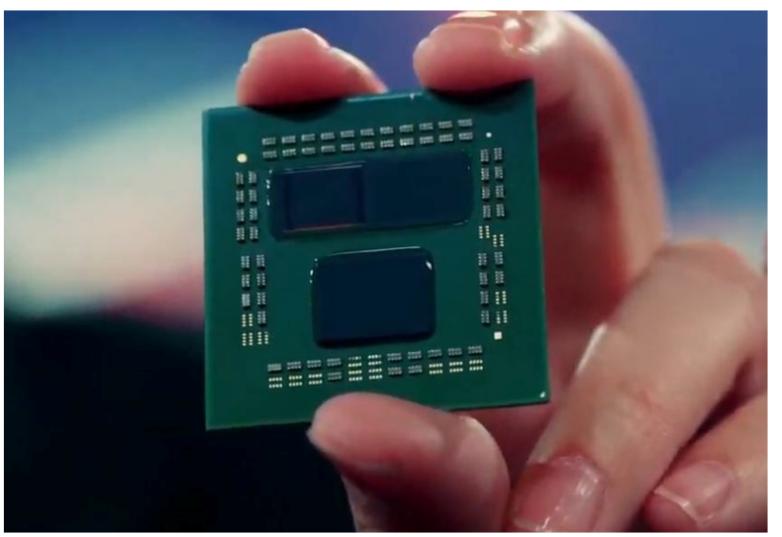

### **AMD's 3D Chiplet**

- AMD's Prototype 95900X chip for gaming

- Gaming performance improvement

- Same 7nm node as Ryzen, but performance gains using chiplet design and 3D copperto-copper hybrid bond

Source: AMD.

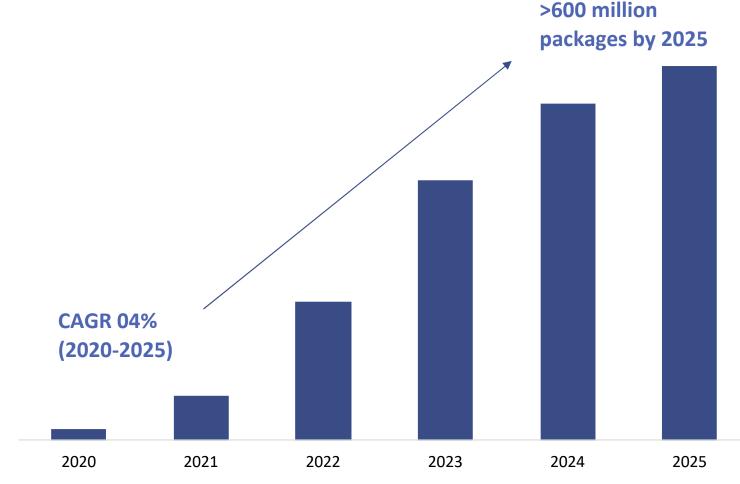

### We Are at the Beginning of Our Journey

- Applications today include server, desktop laptop, networking, Al

- Devices such as GPU, CPU, FPGA

- Future applications expected to include tablets and smartphones

- Introduction of third party IP block providers and standard interfaces potential to broad the market

Source: TechSearch International, Inc.

TechSearch International, Inc.

4801 Spicewood Springs Road, Suite 150

Austin, Texas 78759 USA

+1.512.372.8887

tsi@techsearchinc.com

RELEVANT, ACCURATE, TIMELY

# Thank you sponsors!

# ADVANTEST®

SYNOPSYS®

## Global Companies Rate Advantest THE BEST ATE Company 2021

Advantest receives highest ratings from customers in annual VLSIresearch Customer Satisfaction Survey for 2 consecutive years.

Global customers name Advantest THE BEST supplier of test equipment in 2020 and 2021, with highest ratings in categories of:

Technical Leadership - Partnership - Trust - Recommended Supplier - Field Service

"Year-after-year the company has delivered on its promise of technological excellence and it remains clear that Advantest keeps their customers' successes central to their strategy. Congratulations on celebrating 33 years of recognition for outstanding customer satisfaction."

— Risto Puhakka, President VLSIresearch

# Amkor's Differentiators

#### Technology

Advanced Packaging Leadership Engineering Services Broad Portfolio

#### Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

# SYNOPSYS®

Silicon to Software™

## **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Architecture Workshop** (July 13 & 14, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org