## Road to Chiplets: Architecture July 13 & 14, 2021

www.meptec.org

Meptec Workshop Road to Chiplet: Architecture July 14<sup>th</sup> 2021

### Chiplets & the HIR Village

William (Bill) Chen Ravi Mahajan & WR (Bill) Bottoms

In Collaboration with Heterogeneous Integration Roadmap Technical Working Groups Team

## Agenda

- Covid 19 & Digital Transformation

- Coming to End of Technology Scaling

- Heterogeneous Integration Roadmap

- Chiplet & the HIR Village

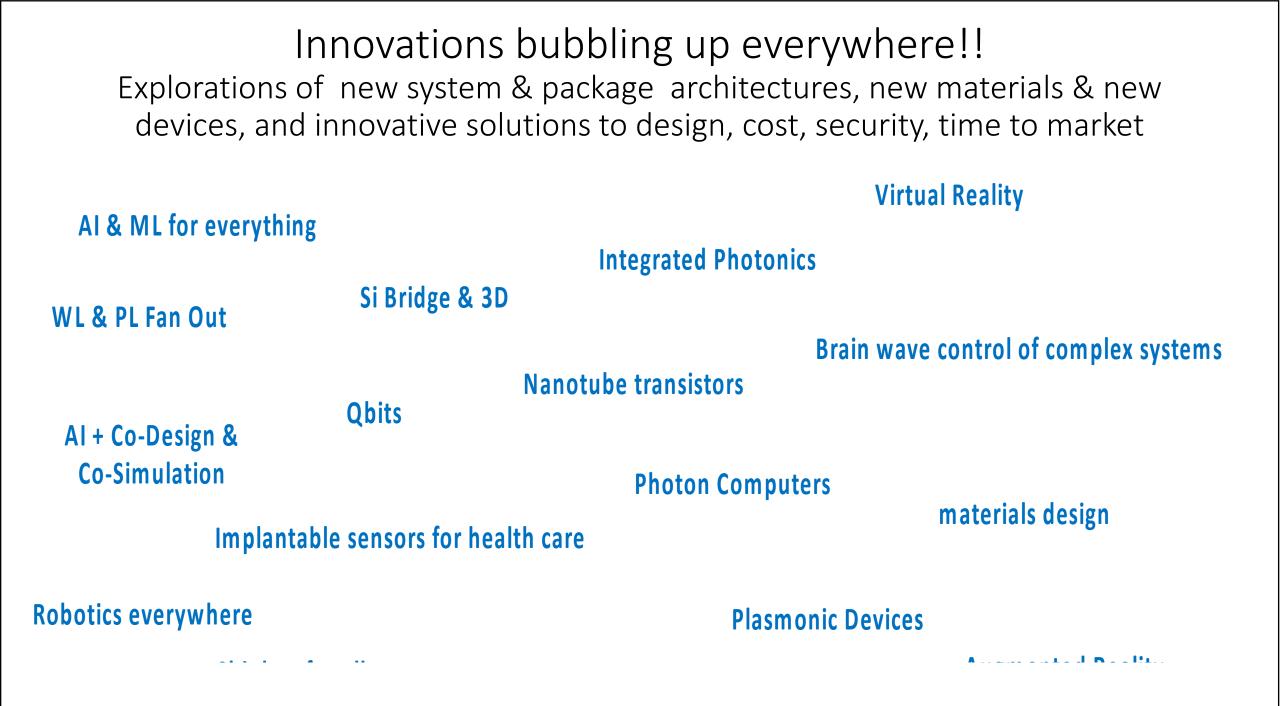

- Innovations bubbling up everywhere

- Summary

### **COVID-19** Pandemic

- As we go through the pandemic, we are seeing millions of infections & staggering loss of life, but also incredible heroism, sacrifice, and resilience.

- The rapid advancement of vaccine science, and comprehensive vaccines deployment are tremendous achievements in global collaboration

- While the Delta Covid Variants are surging, we are hopeful in rapid growth of vaccination. We are optimistic to meet face to face once more not too far into the future

#### 2006 Dec 31

Source 2006 & 2020: Statista & FXSS

- Exxon Mobil

- General Electric

- Gazprom

- Microsoft

- Citicorp

- Bank of America

- Royal Dutch Shell

- BP

- Petro China

- HSBC

### Technology Companies are leading the digital transformation of the global economy and fueling the AI & ML revolution

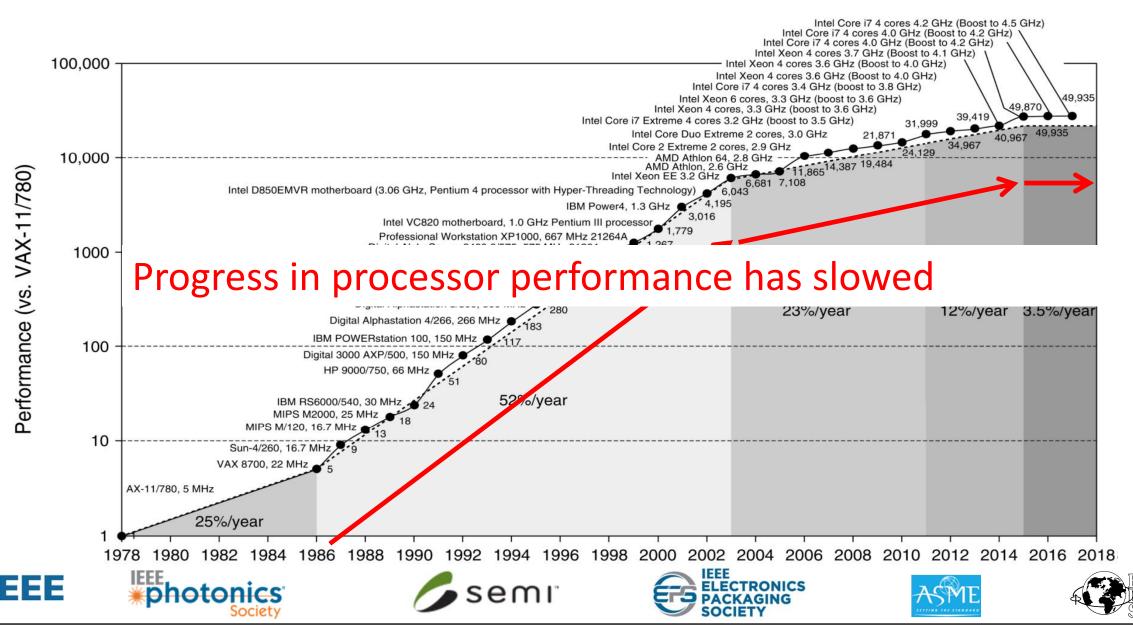

### 40 Years Of Progress In Computing

Source: John Hennessy (Chairman Alphabet) Plenary presentation at DARPA ERI Conference July 23 2018

OCIETY

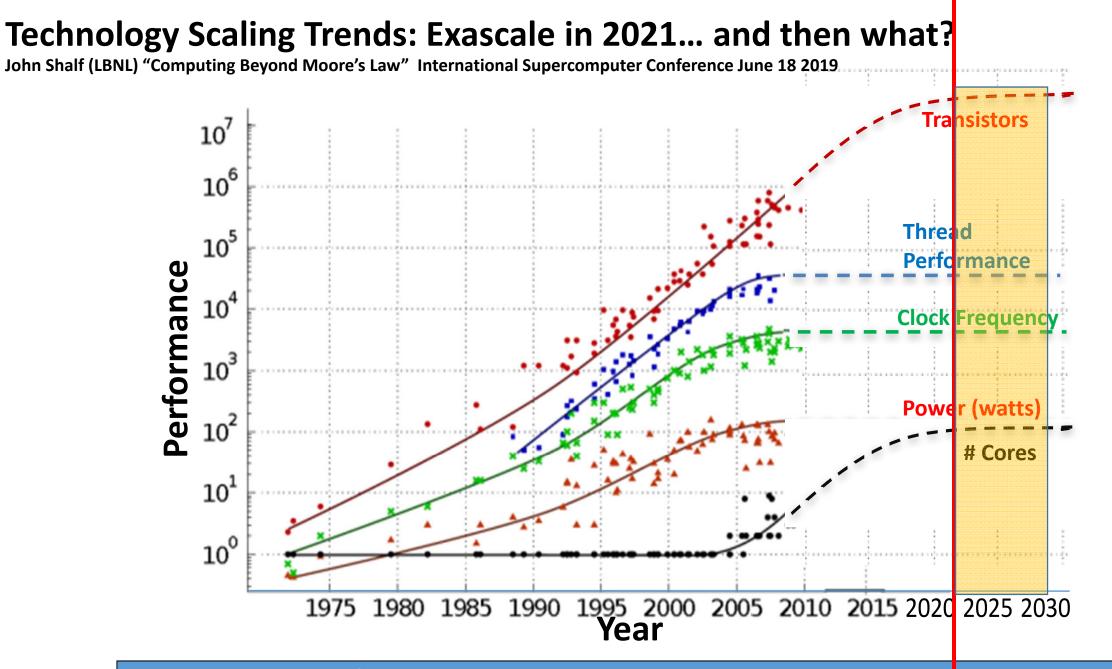

### Moore's Law Economics meeting Headwinds

Source : AMD Lisa Su "Delivering Future of High Performance Computing" Plenary Presentation DARPA ERI Conference July 15, 2019.

Figure courtesy of Kunle Olukotun, Lance Hammond, Herb Sutter, and Burton Smith – extended by John Shalf

## **Technology Roadmapping History**

#### 1991

World's first Open Source Technology Roadmap, the National Technology Roadmap for Semiconductors (NTRS) sponsored by the US Semiconductor Industry Association (SIA).

#### 1998

NTRS expanded forming the first Global Technology Roadmap. Europe, Japan, Taiwan, and Korea joined. It was renamed International Technology Roadmap for Semiconductors (ITRS). 2014

The benefits of Moore's Law scaling diminishing and decision was made to end ITRS.

#### 2016

The last edition of the ITRS was published July 8, 2016

#### **Heterogeneous Integration Roadmap (HIR)**

Launched 10-10-2019 24 chapters 590 Pages Free download Download Link <u>https://eps.ieee.org/technology/hete</u> <u>rogeneous-integration-roadmap</u>

- Sponsored by 3 IEEE Societies (EPS, EDS & Photonics) together with SEMI & ASME Electronics & Photonics Packaging Division

- Comprehensively covering microelectronics technology

ecosystem

- Articulates state-of-the-art Advances in Technology & Science, Future directions, Significant roadblocks & Potential solutions

- HIR is the Knowledge Roadmap & Knowledge Supply Chain for the Heterogeneous Future

#### IEEE Press Release 10-10-2019

PISCATAWAY, N.J.--(BUSINESS WIRE)--IEEE, the world's largest technical professional organization dedicated to advancing technology for humanity, today announced the 2019 release of the Heterogeneous Integration Roadmap (HIR), a roadmap to the future of electronics identifying technology requirements and potential solutions. The primary objective is to stimulate pre-competitive collaboration among industry, academia and government to accelerate progress. The roadmap offers professionals, industry, academia and research institutes a comprehensive, strategic forecast of technology over the next 15 years. The HIR also delivers a 25-year projection for heterogeneous integration of emerging devices and materials with longer research-and-development timelines

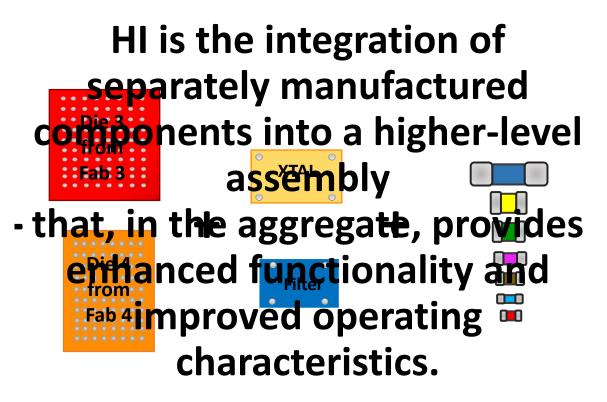

### Heterogeneous Integration:

Heterogeneous by material, component type, circuit type, node and bonding/interconnect method & sources

#### "Cramming More Components onto Integrated Circuits," *Gordon Moore, Electronics*, pp. 114–117, April 19, 1965.

LOG2 OF THE MBER OF COMPONENT INTEGRATED FUNCTI Fig. 3.

#### VII. HEAT PROBLEM

Fig. 2.

Will it be possible to remove the heat generated by tens of thousands of components in a single silicon chip? If we could shrink the volume of a standard highspeed digital computer to that required for the components themselves, we would expect it to glow brightly with present power dissipation. But it won't happen with integrated circuits. Since integrated electronic structures are two dimensional, they have a surface available for cooling close to each center of heat generation. In addition, power is needed primarily to drive the various lines and capacitances associated with the system. As long as a function is confi to a small area on a wafer, the amount of capa which must be driven is distinctly limited. In fa dimensions on an integrated structure make operate the structure at higher spee per unit area

#### VIII. DAY OF RECKONING

Clearly, we will be able to build such componentcrammed equipment. Next, we ask under what circumstances we should do it. The total cost of making a particular system function must be minimized. To do so, we could amortize the engineering over several identical items, or evolve flexible techniques for the engineering of large functions so that no disproportionate expense need be borne by a particular array. Perhaps newly devised design automation procedures could translate from logic

diagram to technological realization without any specia engineering. It may prove to be more economical to build large systems out of smaller functions, whi separately pack aged and interconnected. The availab functions combined with functional design an allow the manufacturer of large system construct a considerable variety of equipment and economically

#### IX. LINEAR CIRCUITRY

sist (

Integration will not change linear systems as radically as digital systems. Still, a considerable degree of integration will be achieved with linear circuits. The lack of largevalue capacitors and inductors is the greatest fun limitation to integrated electronics in the lin By their very nature, such elements r of energy in a volume. For high Q is that the volume be large. The incompati volume and integrated electronics is obvio erms themselves. Certain resonance phenor those in piezoelec tric crystals, can be ave some applications for tuning functions and canacitors will be with us for some

The int mplifier of the future might well constages of gain, giving high performance cost, interspersed with relatively large tuning

er linear functions will be changed considerably. The atching and tracking of similar components in integrated structures will allow the design of differential amplifiers of greatly improved performance. The use of thermal feedback effects to stabilize integrated structures to a small fraction of a degree will allow the construction of oscillators with crystal stability.

Even in the microwave area, structures included in the definition of integrated electronics will become increasingly important. The ability to make and assemble components small compared with the wavelengths involved will allow the use of lumped parameter design, at least at the lower frequencies. It is difficult to predict at the present time just how extensive the invasion of the microwave area by integrated electronics will be. The successful realization of such items as phased-array antennas, for example, using a multiplicity of integrated microwave power sources, could completely revolutionize radar

#### **"VIII. DAY OF RECKONING**

-----The total cost of making a particular system function must be minimized. To do so, we could amortize the engineering over several identical items, or evolve flexible techniques for the engineering of large functions so that no disproportionate expense need be borne by a particular array."

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected. The availability of large functions, combined with functional design and construction, should allow the manufacturer of large systems to design and construct a considerable variety of equipment both rapidly and economically."

**Revisiting Dr Godon** Moore's words today.

A chiplet is a part of a system functional circuit block (SoC) designed to communicate with other chiplets through specific die to die interface. The goal is to manufacture each chiplet economically for optimum cost & performance of the integrated electronics system/subsysteem.

PROCEEDINGS OF THE IEEE, VOL. 86, NO. 1, JANUARY 1998

A visionary message for Chiplets, System-in-Package & Heterogeneous Integration

## The HIR Village

From Wikipedia:

"It takes a village to raise a child" is an African <u>proverb</u> that means that an entire community of people must provide for and interact positively with children for those children to grow and thrive in a safe and healthy environment.

The HIR Village is a community comprising engineers and scientists that voluntarily come together to develop the Heterogeneous Integration Roadmap. It is truly a global village of like-minded people from across diverse disciplines, who all share common vision on maintaining and progressing the Heterogeneous Future for the common good.

### Heterogeneous Integration Roadmap

An Application Driven Roadmap

#### **Market/System Applications**

- High Performance Computing & Data Center

- Mobile

- Medical, Health & Wearables

- Automotive

- IoT

- Aerospace & Defense

#### **Heterogeneous Integration**

#### Components

- Single Chip and Multi Chip Integration (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- 5G Communications & Beyond

#### **Cross Cutting Technologies**

- Materials & Emerging Research Materials

- Emerging Research Devices

- Test

- Supply Chain

- Security

- Thermal Management

- Reliability (under formation)

#### **Integration Processes**

- SiP

- 3D +2D & Interconnect

- WLP (fan in and fan out)

#### **Co-Design & Simulation**

Co-Design & Simulation – Tools & Practice

### Heterogeneous Integration Roadmap

#### An Application Driven Roadmap

#### Market/System Applications

- High Performance Computing & Data Center

- Mobile

- Medical, Health & Wearables

- Automotive

- IoT

- Aerospace & Defense

#### **Heterogeneous Integration Components**

- Single Chip and Multi Chip Integration (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- 5G Communications & Beyond

#### Cross Cutting Technologies

- Materials & Emerging Research Materials

- Emerging Research Devices

- Test

- Supply Chain

- Security

- Thermal Management

- Reliability (under formation)

#### **Integration Processes**

- <mark>SiP</mark>

- 3D +2D & Interconnect

- WLP (fan in and fan out)

#### **Co-Design & Simulation**

Co-Design & Simulation – Tools & Practice

### Heterogeneous Integration Roadmap

#### An Application Driven Roadmap

#### Market/System Applications

- High Performance Computing & Data Center

- Mobile

- Medical, Health & Wearables

- Automotive

- IoT

- Aerospace & Defense

#### **Heterogeneous Integration Components**

- Single Chip and Multi Chip Integration (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- 5G Communications & Beyond

#### Cross Cutting Teeechnologies

- Materials & Emerging Research Materials

- Emerging Research Devices

- Test

- Supply Chain

- Security

- Thermal Management

- Reliability (under formation)

#### **Integration Processes**

- SiP

- 3D +2D & Interconnect

- WLP (fan in and fan out)

#### Co-Design & Simulation

Co-Design & Simulation – Tools & Practice

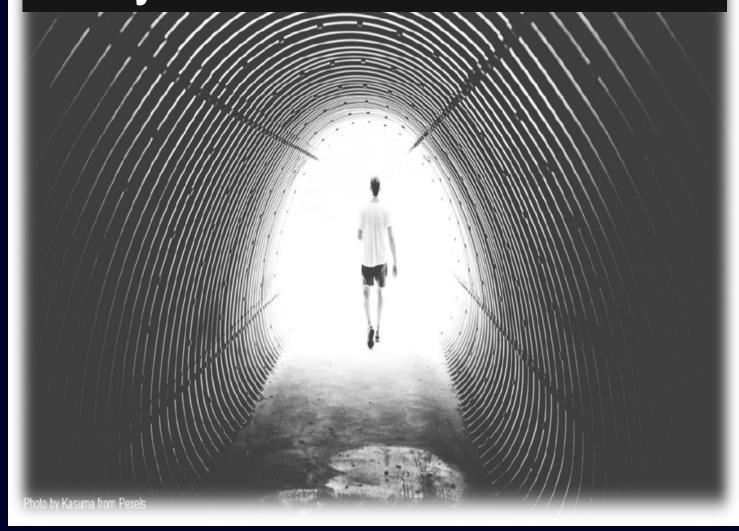

## **Beyond Miniaturization Tunnel**

At 2020 ERI Conference the Plenary Speaker, (Prof Philip Wong, Stanford University, and TSMC Chief Scientist) gave talk "Future is System Integration. He illustrated semiconductor research near the end Moore's Law like a person walking out of a long tunnel seeing green field & sun light.

During Moore's Law time the single focus is miniaturization towards the next set of nodes.

As one emerges from the miniaturization tunnel, opportunities for research outlook & innovations becomes infinitely brighter and broader.

Photo credit: Prof. H.-S.P. Wong, Stanford

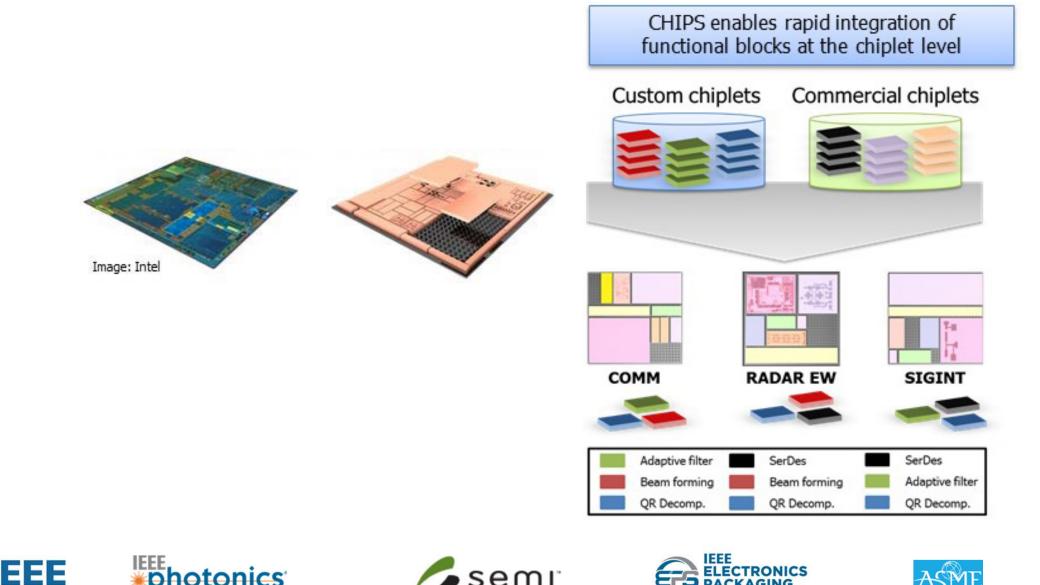

## **DARPA CHIPS Program** Source: "Extending Moore's Law Through Heterogeneous Integration" Andreas Olofsson, SEMICON West July 10, 2020

semi

hotonics

Society

n

CTRONICS

OCIETY

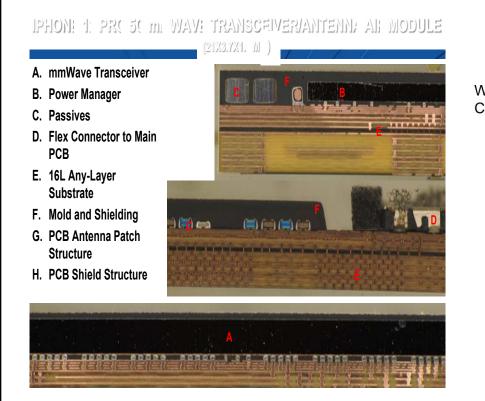

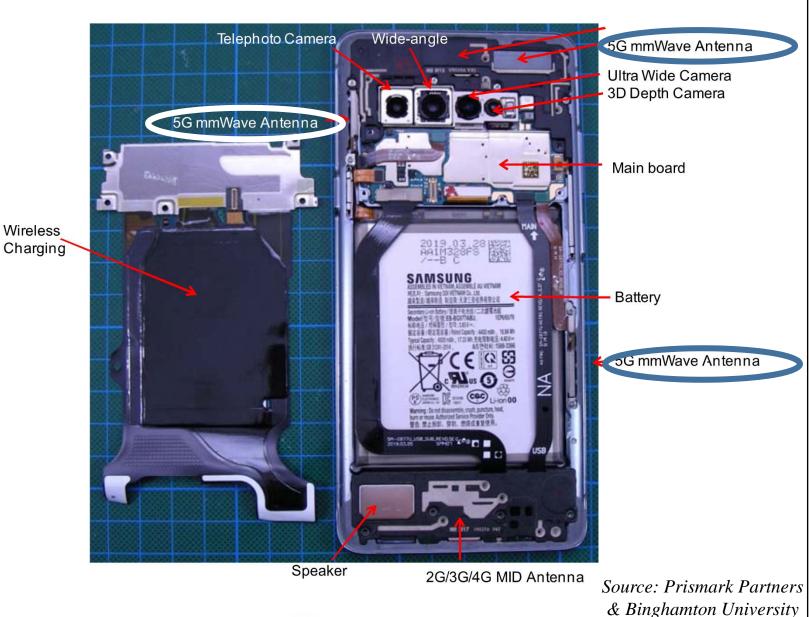

### Two 5G mmWave Antenna Modules

#### SAMSUNG GALAXY S10 mmWave 5G ANTENNA MODULES

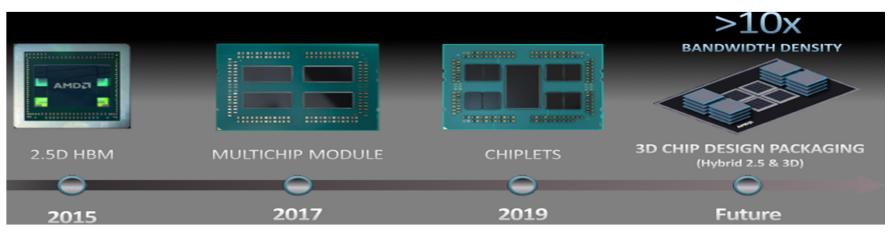

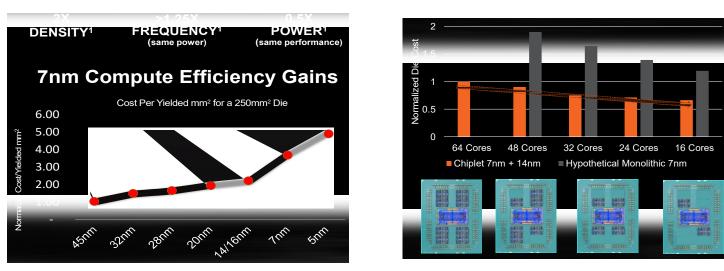

#### Advance Package Integrations at AMD : 2.5D & 1st Gen EPYC MCM

Source: "Chiplets, How to utilize them, what can they do." Dr Bryan Black: IMAPS October 5-8, 2020

SOCIETY

### Adv Package Integrations at AMD : 2<sup>nd</sup> Gen EPYC Chiplets

Source: "Chiplets, How to utilze them, what can they do." Bryan Black: IMAPS October 5-8, 2020

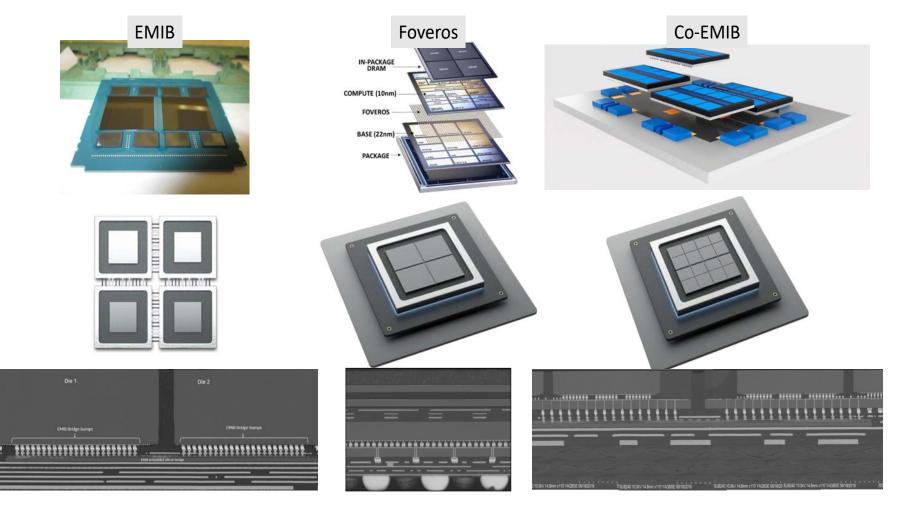

#### Advance Package Chiplet Integration Technologies at Intel: EMIB, Foveros & Co-EMIB

Source: "Adv Package Architecture for Heterogeneous Integration" Ravi Mahajan , Next Gen Electronic System Workshop Binghamton University October 8, 2020. Also Babak Sabi, IMAPS October 5-8 2020

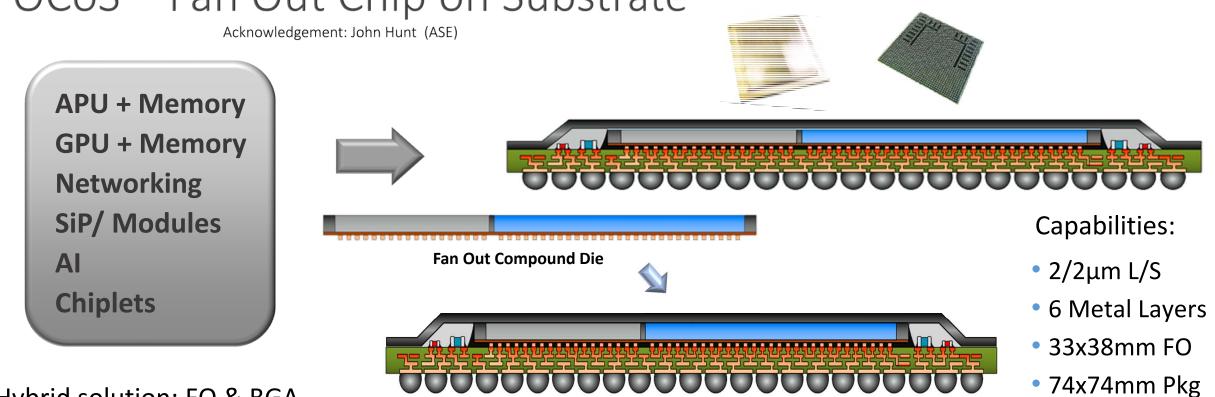

• Hybrid solution: FO & BGA

High density 2D & 3D interconnection in RDL Layers

Advanced Fan Out & FlipChip

• Most complex Fan Out in production

Fan Out Hybrid BGA Package

Multiple products in volume production since January 2016

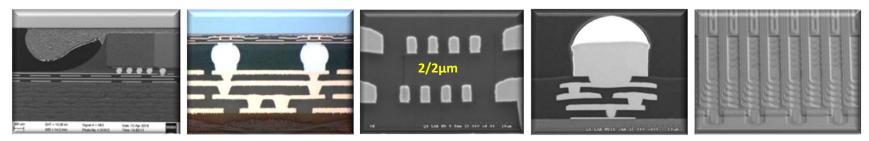

### 2.5D with Si Interposer Source: ASE Group

TSV -

**Compare with Traditional Flip-Chip**

• > 20 times more bumps

**FCBGA**

Fine L/S:

0.5um/0.5um

• 30 times smaller Line/Space between chips

Bump

HBM (High Bandwidth Memory)

GPU/CPU/APU μBump Interposer World's 1<sup>st</sup> 2.5D IC with HBMs **C4**

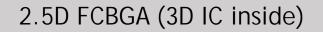

### **Silicon Photonics Co-Package Integration**

Si Photonics Integration Concept. Source: John Shalf (LBNL) [10]

Chapter 9 (Integrated Photonics)

### Summary

- We are at a unique period in time where the global convergence of technology chaos & business disruption are suddenly joined by the Covid 19 Pandemic still spreading around the world.

- There is immense need for a pre-competitive technology roadmap addressing future vision, difficult challenges, potential solutions.

- Chiplet is a powerful technology direction for system/subsysteem integration.

- The HIR Village is is truly a global village of like-minded people from across diverse disciplines, who all share common vision on maintaining and progressing the Heterogeneous Future for the common good.

"We choose to go to the moon in this decade and do the other things, not because they are easy, but because they are hard, because that goal will serve to organize and measure the best of our energies and skills, because that challenge is one that we are willing to accept one we are unwilling to postpone, and one which we intend to win, and the others, too." President John F Kennedy, September 12, 1962

In full acknowledgement of the spirit of dedicated collaboration of Heterogeneous Integration Roadmap Technical Working Groups

### Thank you ALL for Listening

### Thank you sponsors!

# **ADVANTEST**<sub>®</sub>

### **Global Companies Rate Advantest THE BEST ATE Company 2021**

Global customers name Advantest THE BEST supplier of test equipment in 2020 and 2021, with highest ratings in categories of:

**Technical Leadership – Partnership – Trust**

Recommended Supplier – Field Service

"Year-after-year the company has delivered on its promise of technological excellence and it remains clear that Advantest keeps their customers' successes central to their strategy. Congratulations on celebrating 33 years of recognition for outstanding customer satisfaction."

- Risto Puhakka, President VLSIresearch

## Amkor's Differentiators

#### Technology

Advanced Packaging Leadership Engineering Services Broad Portfolio

#### Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship Manufacturing Footprint Local Sales & Support

© 2021 Amkor Technology, Inc.

# **Syndpsys**® Silicon to Software

### **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Architecture Workshop** (July 13 & 14, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

### www.meptec.org