# Road to Chiplets: Architecture July 13 & 14, 2021

# Making Chiplet-based Systems Reliable: Approaches to Support Heterogeneous Integration

Abhijit Dasgupta

Center for Advanced Life Cycle Engineering (CALCE)

University of Maryland, College Park, MD 20742

dasgupta@umd.edu

### **Acknowledgment:**

Richard Rao (Marvell Corporation), Shubhada Sahasrabudhe (Intel)

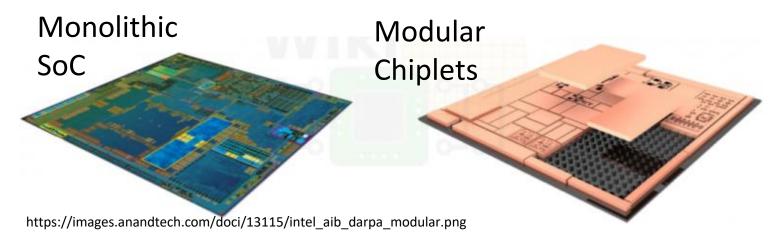

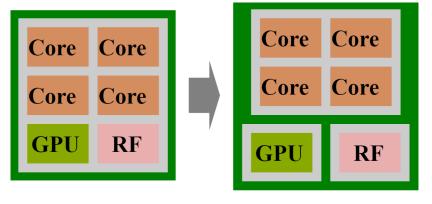

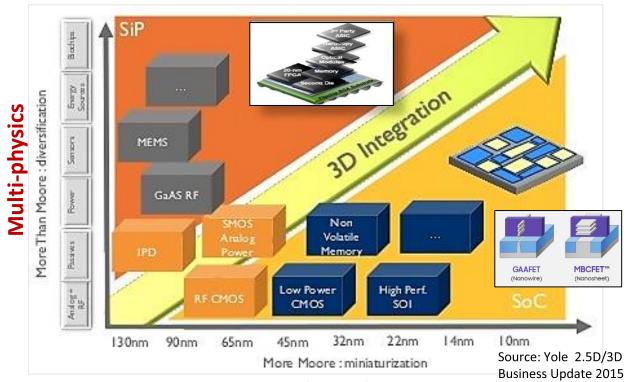

### Chiplets are a critical building block in heterogenous integration:

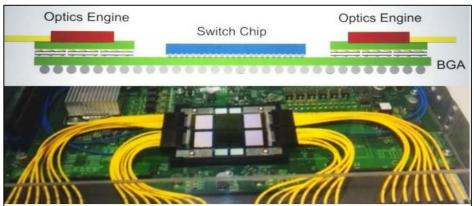

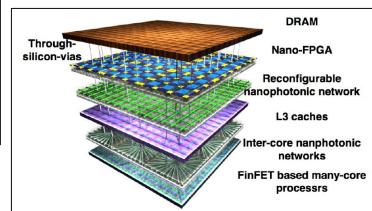

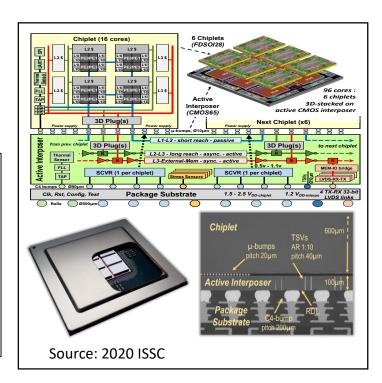

- Electronic (Passive/Active)/photonic/MEMS/Sensor devices

- Digital; Analog; Logic; Memory; Power; RF

- ☐ System, Package (Chiplets) and Wafer levels, including Interconnects and Substrates

- 2.5D and 3D Packaging technologies

# Chiplet architectures bring unique reliability issues

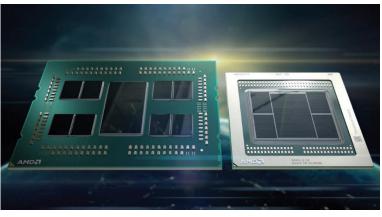

### **AMD**

Intel

https://www.hardwaretimes.com/difference-between-intel-and-amd-ryzen-processors-chiplet-vs-monolithic/

Chiplet-Based Systems: Convergence of Semiconductor & Packaging (Disaggregation and Re-aggregation)

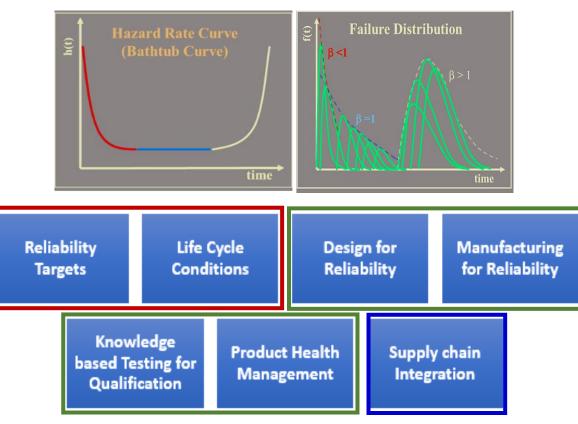

# Approach for reliable chiplet architectures

#### Multi-scale

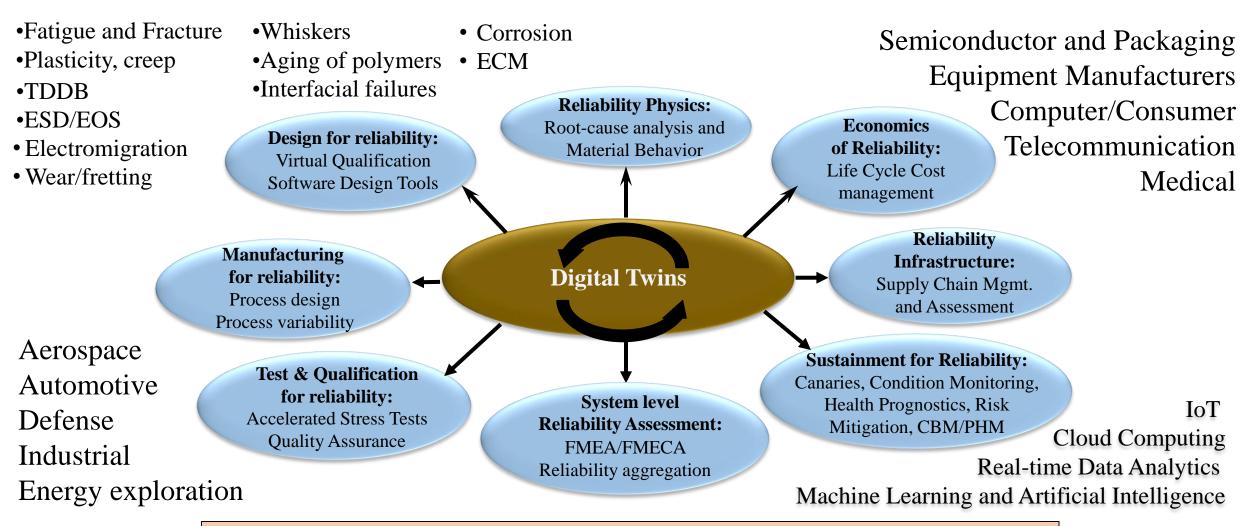

### **Convergence of Semiconductor and Packaging Industries**

### Heterogeneous chiplets:

- technology (IC-node, photonics, MEMS, sensors)

- circuit type (DRAM, Serdes and logic, photonics, power, RF)

- packaging (substrate, interposer and interconnect method)

### **Reliability Assurance Activities**

Reliability of multi-physics/multi-scale HI systems requires holistic cradle-to-grave methodology

# **Chiplet reliability**

Chemica

Intermetallic Growth.

# **Reliability Functions in Product Lifecycle**

### **Proof of Concept**

- New Si and Packaging Technology Understanding

- Feature/performance

- Reliability data collection

- Anticipate new failure modes/mechanisms

- Identify Reliability Risks/FMEA

### **Technical Feasibility**

- Usage stress conditions

- Reliability targets

- Customer engagement

- Reliability/CPI/BLR Risks

Evaluation

- Test Vehicle Design and Corners

- Eng Verification DOE

- Deliver Reliability Design Rule and aging model

- IP Reliability

- Soft errors

### Development/ Design

- DesignVerification

- Implement reliability solutions in the design flow

- Review and assess any violations/trade offs

### Design for Reliability

### **Product Qual**

- Optimize assembly process and materials

- Reliability hardware/dynamic vector/models

- Stress based Qualification

- Knowledge based qualification

#### **HV Production**

- Early failure rate

- Reliability monitoring

- Solve field reliability fails

- Track field failure rate

#### PHM

- Monitor the health of products in field

- Adapt voltage to compensate aging

- Replace failed interconnect

# Designing for reliability: Reliability-physics process

#### **INPUTS**

Hardware configuration

materials, geometry, architecture

### **Life Cycle Loading**

#### **Operational Loads**

Power dissipation, voltage, current, frequency, duty cycle

# **Environmental Loads**

Temperature, relative humidity, pressure, shock.

The life cycle includes transportation, storage, handling and Application environments

### **ANALYSIS**

### Multiphysics "Stress" Analysis

Estimate stresses at failure sites under life-cycle loading:

- Thermal

- Thermo-mechanical

- Vibration-shock

- Hygro-mechanical

- Diffusion

- Electromagnetic

### **Reliability Margins**

Estimate design margins for each relevant failure mechanism due to stresses at each failure site:

- stress margin for overstress mechanisms

- life margin for wearout mechanisms

### **Aggregation to the System Level**

Develop reliability block diagrams

Use Monte Carlo simulations

Use Bayesian updates with field/test data (if any)

### **Sensitivity Analysis**

Evaluate sensitivity of the product durability to changes in: application, design, manufacturing window, life-cycle support methodologies

#### **OUTPUTS**

Ranking of potential failure mechanisms and sites

Design tradeoffs

Risk mitigation solutions

Accelerated test conditions

Reliability Assessment

Health Prognostics

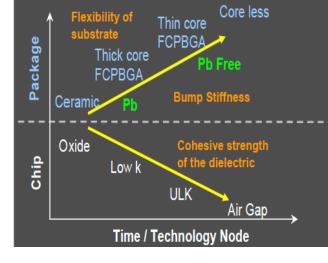

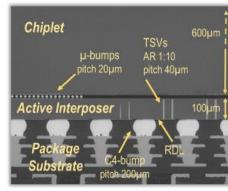

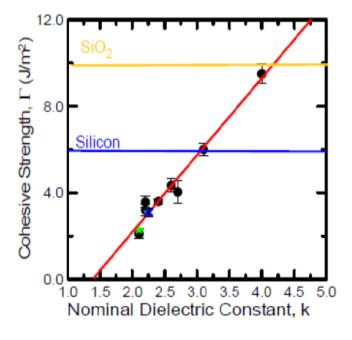

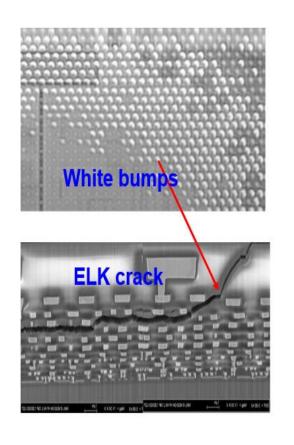

# **Advanced chiplets: CPI challenges**

- ☐ CPI issues are increasing with newer Si nodes

- ☐ Device and packaging reliability were treated separately in old nodes

- ☐ Advanced Si with low k, CPI requires co-development of device and package

- ☐ Low k and Ultra low k introduction

- ☐ Fragile and poor adhesion

- ☐ Build up substrate

- ☐ High CTE and warpage

- ☐ Pb free or Cu pillar interconnect

- ☐ Higher modulus

- ☐ Complex die

- ☐ Big die size

- ☐ Higher power

- ☐ Bump on trace

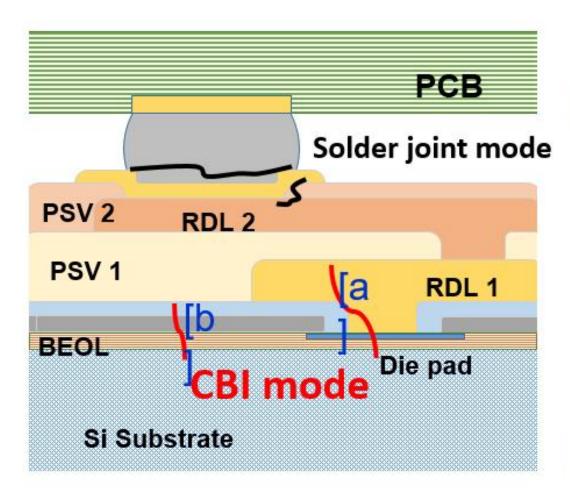

- ☐ More advanced packaging induced board-chip-package interaction

- WLP

- □ 2.5D/3D

- ☐ Big FCBGA

# Chiplets: An overview of 3D IC stresses and reliability

- Stress induced by Cupillars on low-K

- Stress induced by overmold, laminates CTE mismatch

•...

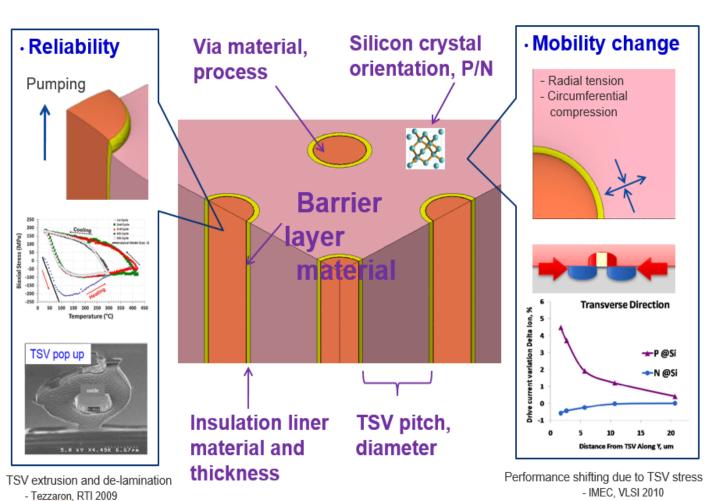

# Impact of TSV/uBump on top die

- Built-in stress

- Stress varies as function of temperature

Die 2

# Impact of 3D-SIC bonding on dies

- Stress during bonding

- Stress due to underfill

CTE mismatch

•...

### **Microbumps:**

- Material anisotropy

- Length-scale effects

- Releases stress

- Strength of die

• ...

# Impact of TSV on bottom die

- Built-in stress

- •Stress varies as function of temperature

• ...

### Stress/strain can lead to

- mechanical failures due to delamination, peel, fatigue, ...

- electrical impact due to parameter shifts, increased variability, EM,...

Multi-scale

**Source: IMEC**

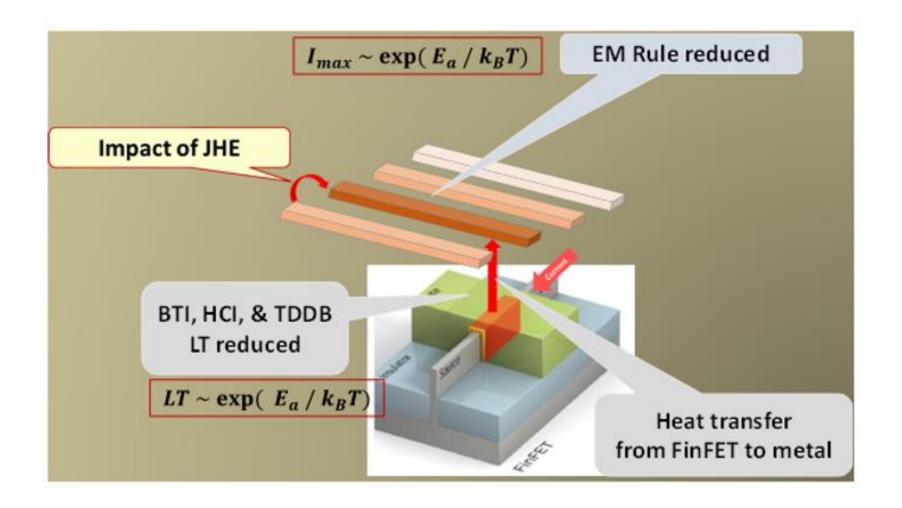

Electromigration

Bias Temperature

Instability

Hot carrier Injection

Time-Dependent

Dielectric

Breakdown

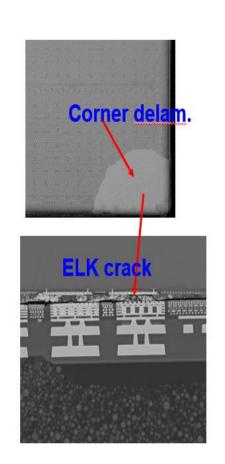

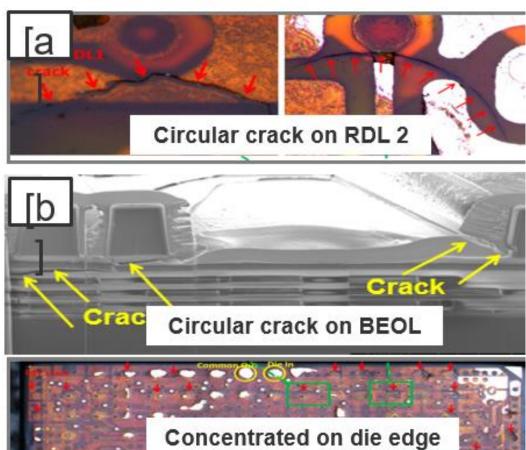

### Typical CPI-induced MEOL/BEOL failure modes

**Source: Synopsys**

Source: IBM

### **CBPI-induced failure modes**

Meditek, 2017 IRPS

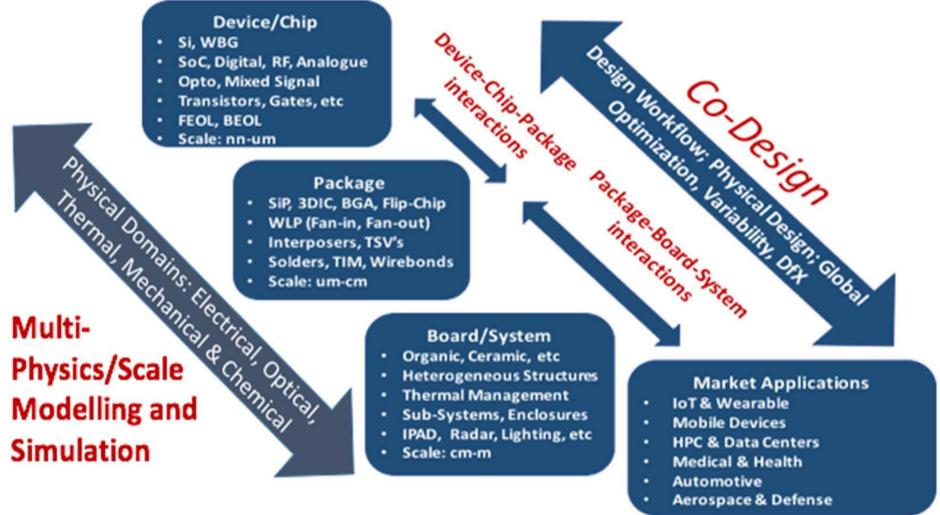

# Chiplets: Physics-based modeling simulation and co-design

Source: HIR; Modelling and Simulation TWG

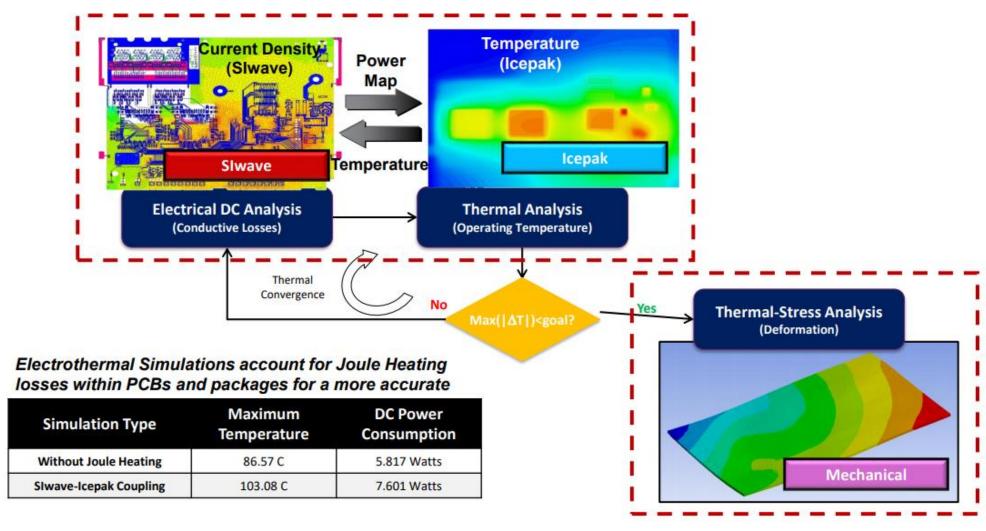

# System-level multiphysics simulations

**Source: ANSYS**

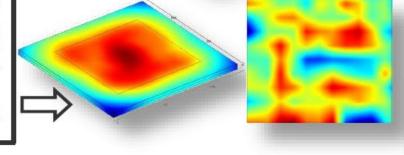

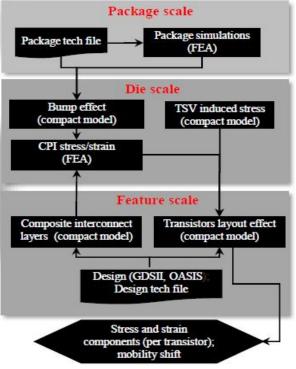

# Multi-scale and multi-physics CPI flow

#### Package-scale simulation (FEA)

<u>Input</u>: geometry; material properties; smeared mechanical properties for RDLs, Silicon/TSV bulk, interconnect.

<u>Output:</u> field of displacement components on the die faces.

# ent

### Die-scale simulation (FEA)

<u>Input:</u> geometry; field of displacements on the die faces; coordinate-dependent mechanical properties for RDLs, Silicon/TSV bulk, interconnect.

<u>Output:</u> Distribution of the strain components across device layer.

# Layout-scale w/feature-scale resolution (compact model):

<u>Input:</u> GDS; distribution of the strain components across device layer.

**Output:** Transistor-to-transistor variation in stress components

**Source: Mentor Graphics**

### Modes/Mechanisms/Models for Degradation & Failure

| <b>Multiphysics</b> |                | Multiscale<br>Integration | Multi Physics                                                                   | Electrical Stress                                                                                |                                                                                                                             | SI/PI (Electrical<br>Performance)                                             | Thermal Analysis                                                                              | Moisture                                                                                                |                                                                                                                    | Thermal Mechanical Stress                                                                                                                                                                                                    |                                                                                                                                 | Mechanical Stress                                                               |                                                                                                                                      | Thermal<br>Interaction<br>with SI/PI                               | Stress<br>Interaction<br>with SI/PI                      | Simulation/Modelling and Co-C                                                                                          |                                                                                                     | nign Flows                                                                                                                                                                       | Manufacturing<br>Variability | Material<br>Property<br>and<br>Variability |

|---------------------|----------------|---------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------------------------------------|

|                     |                |                           |                                                                                 | Failure Modes                                                                                    | Failure Mechanism<br>and Reliability Models                                                                                 |                                                                               |                                                                                               | Failure Modes                                                                                           | Failure Mechanism<br>and Reliability<br>Models                                                                     | Failure Modes                                                                                                                                                                                                                | Failure Mechanism and<br>Reliability Models                                                                                     | Failure Modes                                                                   | Failure Mechanism<br>and Reliability<br>Models                                                                                       |                                                                    |                                                          | Failure Modes                                                                                                          | EDA flows                                                                                           | PDK/ADK                                                                                                                                                                          |                              |                                            |

| Multiscale          | Devices        | Transistor                | FinFET and GAA                                                                  | Leakage current,<br>ripple currents,<br>unstabel<br>performance and<br>ESD                       | N/PBTI models with<br>recovery; HCI model;<br>TDDB Weibull model;<br>Oxide & junction<br>breakdown model                    | Transistor<br>SPICE                                                           | FinFET SHE                                                                                    | No known fallures                                                                                       | None                                                                                                               | FinFET SHE channel stress;<br>µBump/C4 bump/TSV; system<br>level stresses                                                                                                                                                    | FinFET SHE Models; CPI<br>Model; Piezo-electrical<br>models                                                                     | No known<br>failures                                                            | None                                                                                                                                 | SHE effect on<br>SPICE<br>parameters                               | Influence of<br>Si stress on<br>SPICE<br>paramters       | Effects of<br>degradation<br>mechanisms and<br>process variabilities<br>on electrical<br>functionality                 | Cadence; Relxpert;<br>Mentor Graphics                                                               | Integrate of<br>degradation models<br>into Device SPICE<br>Model                                                                                                                 |                              |                                            |

|                     | Interconnects  | Interconnects             | MEOL/BEOL<br>Metal/Via /ELK                                                     | Electromigration;<br>Inter Layer<br>Dielectric ELX<br>Breakdown; MEOL<br>Oxide Breakdown;<br>EOS | Electromigration<br>model; Dielectric<br>breakdown model                                                                    | Extraction of<br>RLC Model                                                    | Joule Heating<br>simulation; SHE<br>effects on<br>MEOL/BEOL                                   | Pad and underline<br>metal prosion;<br>Cu/ELK<br>delamination<br>3. Cu loss/diffusion                   | Electrochemical<br>comosion; interface<br>degradation due to<br>moisture<br>absorption; Barrier<br>metal oxidation | SHE failure in Cu/ELK, MEOL, BEOL,<br>µBump, TSV; RDL failures from<br>package stress, Cu fatigue;<br>LowK/ELK layer cracking &<br>delamination                                                                              | Creep induced voiding: CTE<br>mismatch; SHE induced<br>localized thermal cycling                                                | LowK/ELK<br>layer cracking<br>&<br>delamination                                 | fatige by bending                                                                                                                    | Joule/SHE<br>temp effects<br>on RLC                                | Effect of<br>Cu/ELK stress<br>on RLC                     | CPI induced Cu/ELK<br>cracking: JHE/SHE<br>stresses; stress from<br>bumps/TSV/RDL &<br>Packaging                       | Ansys Mentor                                                                                        |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | FBECL<br>RDL/Dielectric                                                         | RDL/UBM<br>Electromigration                                                                      | Electromigration                                                                                                            | Extraction of<br>RDL RLC Model                                                | BEOL Joule/SHE<br>effect on RDL<br>temperature                                                | Cu dedrite                                                                                              | Electro-chemical corrosion                                                                                         | RDL cracking                                                                                                                                                                                                                 | μbump/TSV/Package/<br>Board effects on RDL stress                                                                               |                                                                                 |                                                                                                                                      | Effect of RDL<br>temp on<br>electrical<br>model                    | Effect of RDL<br>stress on<br>electrical<br>model        | CPL/CBPI induced<br>failures: RDL cracking<br>& delamination                                                           | Effect of temp and stress on RDL EM                                                                 |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | Au/Cu<br>Wirebonding                                                            | Electromigration                                                                                 |                                                                                                                             |                                                                               |                                                                                               | IMC Corrosion                                                                                           |                                                                                                                    | Bond wire fatigue                                                                                                                                                                                                            |                                                                                                                                 | Cu/ELK<br>cracking                                                              | Bonding force<br>models                                                                                                              |                                                                    |                                                          |                                                                                                                        |                                                                                                     |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | μΒυπρ/C4<br>Bump/UBM                                                            | Electromigration<br>induced voids                                                                | Black's model;<br>Mutiphysics EM model<br>induding eletron,<br>thermal gradient,<br>stress gradient and<br>atomic diffusion | μbump<br>electrical<br>model                                                  | Die Internal Joule/SHE temp effect & external temp effect on bump temperature                 | UBM delamination                                                                                        | Galvanic effect<br>(electro-chemical<br>reaction)                                                                  | Bump Joint cracking;<br>Under Bump ELK cracking; Under<br>pad cracking in substate                                                                                                                                           | CTE mismatch induced stress;<br>Fatigue                                                                                         | Tensile stress<br>causes bump<br>peel; cracks at<br>µbump; UBM<br>and interface | Fracture/fatigue<br>from shock, drop,<br>impact, Wbr; e.g. in<br>die attach, dielectric<br>layer, inter-poser,<br>UBM, solder joints | Effect of temp<br>on bump<br>electrical<br>model                   | Effect of<br>bump stress<br>on electrical<br>model       | Multi Physics Bump<br>EM - local current,<br>temp, temp gradient<br>and stress effect on<br>ubump EM                   | Bump fatigue: effect<br>of local temp &<br>stress on fatigue life                                   |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | TSV/Interposer/<br>EMIB                                                         | Electromigration;<br>Barrier Dielectric<br>breakdown                                             | Black's model;<br>Mutiphysics EM model<br>induding eletron,<br>thermal gradient,<br>stress gradient and<br>atomic diffusion | TSV electrical<br>model                                                       | Internal Joule/SHE<br>temp effect on the<br>TSV temp;<br>External temp effect<br>on TSV temp. |                                                                                                         |                                                                                                                    | Cu pumping/TSV pop up                                                                                                                                                                                                        | Cu extraion due to CTE<br>mismatch with Si;<br>plastic rachetting at high<br>temp                                               |                                                                                 |                                                                                                                                      | Effect of TSV<br>temp on<br>electrical<br>model                    | Effect of TSV<br>stress on<br>electrical<br>model        | TSV EM response to<br>local current, temp<br>field and stress; TSV<br>Pop out and effects<br>on TSV/Si<br>delamination | Barrier breakdown -<br>How does<br>voltage/current,<br>temp and stress<br>affect TSV barrier<br>BD? |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | Passivation                                                                     | Passivation<br>cracking                                                                          | EOS induced cracking                                                                                                        |                                                                               |                                                                                               | Passivation cracking<br>& delamination;<br>underfil/Mold<br>compound<br>delamination                    |                                                                                                                    | Passivation cracking                                                                                                                                                                                                         | CPI stress in SIN                                                                                                               |                                                                                 |                                                                                                                                      |                                                                    |                                                          |                                                                                                                        |                                                                                                     | fracture criteria; Vold<br>initiation and<br>propagation criteria;<br>Interconnect<br>fatigue/creep model;                                                                       |                              |                                            |

|                     | Packaging/     |                           | Underfill                                                                       |                                                                                                  |                                                                                                                             |                                                                               |                                                                                               | Underfill to<br>die/substrate<br>delamination;<br>underfill swelling                                    | Moisture<br>degradation in<br>underfill & at<br>interfaces                                                         | Bump joint cracking                                                                                                                                                                                                          | Solder joint fracture and fatigue due to underfill expansion                                                                    |                                                                                 |                                                                                                                                      |                                                                    |                                                          |                                                                                                                        |                                                                                                     | Picking Interface<br>fracture ordinary<br>Mohammar diffusion<br>and upon pressure<br>model; IMC<br>tharmal/machylelactic<br>at a propertise;<br>Photonica optical<br>properties. |                              |                                            |

|                     |                |                           | High Density<br>Substrate                                                       | Metal trace<br>electromigration                                                                  |                                                                                                                             | Package<br>Substrate RLC<br>model<br>extraction                               | Co-thermal sim<br>from die to package                                                         | Metal trace<br>corrosion                                                                                |                                                                                                                    | Metal trace/via cracking                                                                                                                                                                                                     |                                                                                                                                 |                                                                                 |                                                                                                                                      | Thermal -<br>electrical<br>perfromance<br>interactions             | Mechanical-<br>electrical<br>performance<br>interactions | Cu trace EM - effect<br>of local current, temp<br>and stress                                                           | Thermal & mechanical effect on Cu trace/via cracking                                                |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | Wafer Level<br>Package                                                          |                                                                                                  |                                                                                                                             |                                                                               |                                                                                               |                                                                                                         |                                                                                                                    | Warpage                                                                                                                                                                                                                      |                                                                                                                                 |                                                                                 |                                                                                                                                      |                                                                    |                                                          |                                                                                                                        |                                                                                                     |                                                                                                                                                                                  |                              |                                            |

|                     | System         |                           | Fanout Package<br>2.x/2.5D<br>Interposer<br>Package<br>(CoWoS and<br>EMIB, etc) |                                                                                                  |                                                                                                                             |                                                                               |                                                                                               |                                                                                                         |                                                                                                                    | Warpage Warpage; Embedded die delamination from substrate & sidewall; pvia & pbump cracking & delamination; Solider/TIM delamination                                                                                         |                                                                                                                                 |                                                                                 |                                                                                                                                      |                                                                    |                                                          |                                                                                                                        |                                                                                                     |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | 3D Package<br>(Foveros, etc)                                                    |                                                                                                  |                                                                                                                             | Mold<br>compound pop<br>corn;<br>Anisotropic<br>conductive<br>adhesive cracks |                                                                                               | Mold compound pop-coming                                                                                |                                                                                                                    | FinFET ion shift (due to TSV/SI CTE<br>mismatch, µBump stress, shrinkage<br>of underfill & EMCL; TSV effects on<br>BTU/NC; BEOL cracking Cu pillar<br>joint failure; Mold compound pop-<br>com; conductive adhesive cracking |                                                                                                                                 |                                                                                 |                                                                                                                                      |                                                                    |                                                          |                                                                                                                        |                                                                                                     |                                                                                                                                                                                  |                              |                                            |

|                     |                |                           | Chiplet/KGD                                                                     | ESD                                                                                              |                                                                                                                             |                                                                               |                                                                                               |                                                                                                         |                                                                                                                    | Die edge cracking: Under bump EU<br>cracking                                                                                                                                                                                 |                                                                                                                                 |                                                                                 |                                                                                                                                      |                                                                    |                                                          |                                                                                                                        |                                                                                                     |                                                                                                                                                                                  |                              |                                            |

| N                   | /lodule/System | Module/ System            | Printed Circuit<br>Board Assembly                                               | Leakage current<br>and shorts from<br>Conductive<br>filament<br>formation                        | electro-chemical metal<br>migration                                                                                         | PCB Board<br>electrical<br>model                                              | \Co-thermal sim<br>from die to package<br>to system                                           | leakage current and<br>shorts from loss of<br>surface insulation<br>resistance &<br>conductive filament | moisture ingress,<br>leading to fiber-<br>matrix debonding,<br>and electro-chemical<br>metal migration             | Solder joint cracking; Cracking of<br>PTH plating; PCB delamination;<br>trace cracking; Warpage                                                                                                                              | thermomechanical fatigue<br>of trace and solder, IMC<br>fracture; CTE mismatches<br>between: component /<br>PWB, metallization/ | Solder joint<br>cracking: pad<br>cratering                                      | Stress exceeds the material and interface strength                                                                                   | Effects of PCB<br>temp and<br>corrosion on<br>electrical<br>model? | Effects of PCI<br>stress on<br>electrical<br>model?      | Board level Solder<br>Joint Reliability                                                                                | ANSYS Mechanical                                                                                    | PCB thermal/ mechanical<br>properties; Solder joint<br>fatigue/creep model;<br>Solder joint dyannic/<br>properties                                                               |                              |                                            |

# Chiplet reliability assessment capabilities: status

| Key Elements for DfR Flow                  | Wafer Level DfR                                                                                                                                   | Package and System Level DfR                                                                                                                                                                                       | Chip to Package to Board Interactions                                               |

|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| key Elements for Dik flow                  | Water Level DIK                                                                                                                                   | r ackage and System Level Dik                                                                                                                                                                                      |                                                                                     |

| Electrical and Thermal Stress              | Localized Self Heating and hot spots                                                                                                              | Global Level thermal managements                                                                                                                                                                                   | FEOL/BEOL and systeme level thermal interactions                                    |

| Failure Modes                              | TDDB, HCI, BTI , EM and SM, etc                                                                                                                   | Warpage, delamination; C4, ubump,<br>DBI, TSV, Optical Via interconnect<br>fatigue and migration failure, etc                                                                                                      | Global and local Stress effects on Cu/ELK failure, stress effects on FET's mobility |

| Failure Mechanism and<br>Reliability Model | Weibull, Lognormal, Power Law Model,<br>Aging Model, etc                                                                                          | Weibull, Lognormal, multiphysics<br>models, etc; many are under<br>development                                                                                                                                     | Under development                                                                   |

| Material Chaterization and<br>Modeling     | Modeling device thermal characteristics (Thermal resistance) Modeling device aging Modeling the impact of stress on device threshold, delay, etc. | To make materials data useable by EDA tools – and enable them to produce accurate and meaningful results – materials data needs to be presented in a machine-readable format and agreed upon with EDA tool vendor. | Modelling multi scale and multi physics failures                                    |

| Process Design Kit (PDK)                   | Foundry Design Kit                                                                                                                                | Assembly Process Design Kit                                                                                                                                                                                        | Under development                                                                   |

| EDA Flow                                   | Cadence Spectre/HSPICE, etc                                                                                                                       | Ansys/Mentor, etc                                                                                                                                                                                                  | Mentor/Synopsys                                                                     |

| Circuit/System Reliability                 | HCI/BTI and EM Available; TDDB and SM not Available                                                                                               | Under development                                                                                                                                                                                                  | Under development                                                                   |

|                                            |                                                                                                                                                   |                                                                                                                                                                                                                    |                                                                                     |

| Established                                |                                                                                                                                                   |                                                                                                                                                                                                                    |                                                                                     |

| Partially Established                      |                                                                                                                                                   |                                                                                                                                                                                                                    |                                                                                     |

| Under development or Not<br>Available      |                                                                                                                                                   |                                                                                                                                                                                                                    |                                                                                     |

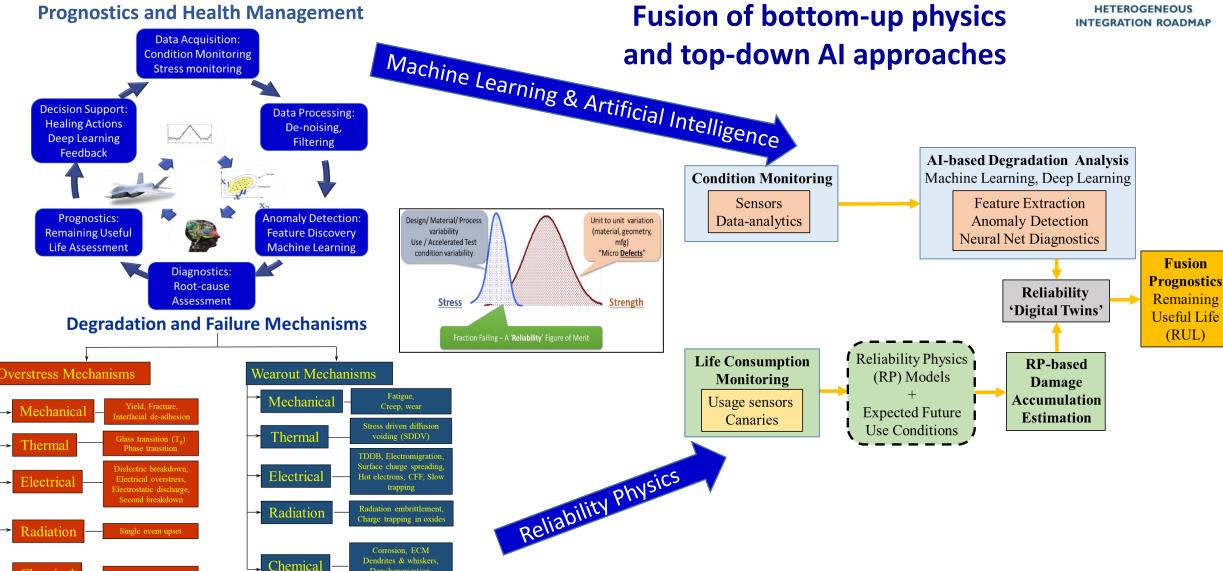

# Qualification and testing: Reliability validation/verification

The changing and challenging landscape

Need for dynamic, flexible models and methods

Extreme environments Extreme usages/ lifetime

Latest tech nodes

Diverse components

New failure modes

Wide range of Rel tests

Innovative FA/FI

Stochastic modeling

Field Telemetry

Reliability Physics

Test time optimizations Digital Twin feedback dool

Multi-physics methods to quantify 'stress' and

'strength' distributions at potential sites of failure

Qualification testing

needs to be Customized. Knowledge-based and **Innovative**

Data feedback loop with Digital Twins to validate failure characteristics and run virtual experiments

Integrated PHM - Selfcognizant, intelligent, bio-mimetic hardware to 'age with grace'

Source: Sahasrabudhe (Intel)

# **Summary: Reliable Chiplets and HI Systems**

# HETEROGENEOUS INTEGRATION ROADMAP

### Convergence of Reliability-Physics (RP) and Artificial Intelligence (AI)

Intelligent, resilient, self-cognizant, self-healing chiplet-based HI systems

# Thank you sponsors!

# ADVANTEST®

SYNOPSYS®

# Global Companies Rate Advantest THE BEST ATE Company 2021

Advantest receives highest ratings from customers in annual VLSIresearch Customer Satisfaction Survey for 2 consecutive years.

Global customers name Advantest THE BEST supplier of test equipment in 2020 and 2021, with highest ratings in categories of:

Technical Leadership - Partnership - Trust - Recommended Supplier - Field Service

"Year-after-year the company has delivered on its promise of technological excellence and it remains clear that Advantest keeps their customers' successes central to their strategy. Congratulations on celebrating 33 years of recognition for outstanding customer satisfaction."

— Risto Puhakka, President VLSIresearch

# Amkor's Differentiators

# Technology

Advanced Packaging Leadership Engineering Services Broad Portfolio

### Quality

QualityFIRST Culture Execution Automation

### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

# SYNOPSYS®

Silicon to Software™

# **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Architecture Workshop** (July 13 & 14, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org