## Too Hot To Test

February 9 - 11, 2021

www.meptec.org

### **System Power Modeling and Analysis for Test**

David Ratchkov

CEO/Founder

david@thracesystems.com

https://thracesystems.com

2/10/2021

### Introduction

CEO of Thrace Systems, focuses on System Power EDA

Co-chair of CDX (Chiplet Design Exchange) workstream under OCP ODSA

Previously 18 years and Broadcom/Avago/LSI/LSI Logic

Responsible for power tools and methodology

#### **Product line**

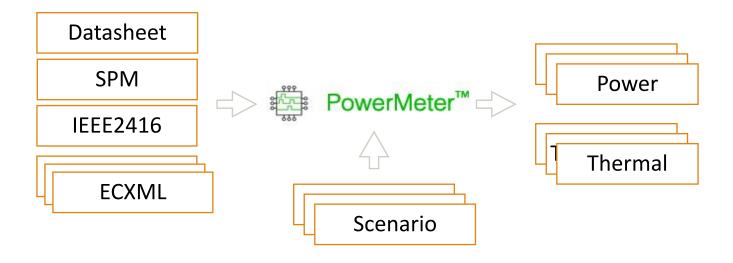

PowerMeter<sup>™</sup> is a comprehensive and collaborative power analysis platform for System Level Power Analysis

Cloud-native for best-of-class collaboration and concurrent analysis

IEEE2416 model generator

Design Dashboard Engine

### Agenda

#### **Power and Thermal Analysis Overview**

Objectives

**Definitions**

System Level Power models

**Flows**

#### Models in action

Chiplet system power and thermal models and results

#### Q&A

### Objectives of Power and Thermal Analysis

#### Resolve Thermal concerns

Need to know sequence, location, amount and duration of power dissipation

#### Power supply concerns

Need to know worst case current draw and current draw change

#### **Battery concerns**

Need to know energy consumption over very long period of time

### Flow and model needs: What is your System?

#### **System**

Any configuration of elements outside of a unit's power supplies

This includes supplies, boards, connectivity, packaging, other components inside or outside of the package, or lack of them

#### **Scenario**

A full set of configuration parameters to describe a single unit of operation

This includes voltage levels, ambient temperatures, modes of operation

### Flow and model needs: What is your System?

## Planning for Test needs to start as early as architecture level

Plan supplies (System)

Plan thermal aspects of system, both application and test (System)

Plan test flow and sequences (Scenarios)

#### Sets a baseline electrical and thermal constraints

#### **Need flexible System Power Models**

Maintain compatibility over time and between flows

Modeling parameters outside of typical bounds

### System Power Model (SPM)

## Thrace System's System Power Model works from pre-RTL architecture level to post-Si analysis

Designed with "any-system" in mind

Maintains historical learnings through technology mapping

#### Higher level of abstraction modeling than classic models (Liberty)

Can model almost anything - regulators, SERDES, transaction power

Designed to scale to handle large and complex systems

#### **Includes support for IEEE2416 Power Contributors**

Announced at DAC'20 first production IEEE2416 generator as part of PowerMeter See Tutorial replay here https://si2.org/dac-upm-tutorial/

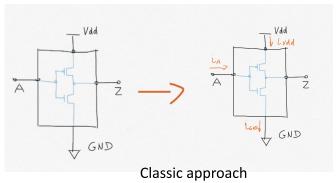

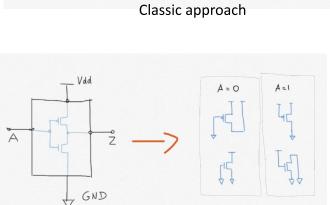

### Introduction to IEEE2416

**IEEE2416 Power Contributor**

Classic approach to power modelling (Liberty)

Capture boundary pin currents at a fixed

Process, Voltage and Temperature

PROS: Very Simple models

CONS: Fixed value, not possible to vary P,V,T,

need a new model

IEEE2416 approach targets variable Process, Voltage and Temperature post model generation

- Capture circuit details, estimate leakage later PROS:

- Designed with variable P,V,T in mind End-user can vary P,V,T

### **CDX** Reference flow

#### **ODSA CDX workstream**

- Focus on flow pipe clean and PoC

- Design data seeded by zGlue OmniChip Reference Design

#### Si2 UPM workgroup

Focus on IEEE2416 "IEEE Standard for Power Modeling to Enable System Level Analysis", aka UPM

#### **JEDEC**

- Released ECXML spec in Sept'20

#### Chiplet power data

- Extract information from datasheet

- Provide SPM, when available

- ECXML

#### Power analysis

- Scenarios and System information

- Use PowerMeter<sup>™</sup> to perform system-level power analysis

- Generate SPM, if needed

- Generate ECXML

#### Thermal analysis

### Reference Flow

Concurrent Multi-Mode Multi-System functional and test power and thermal analysis

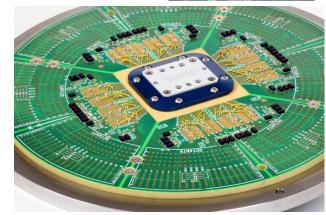

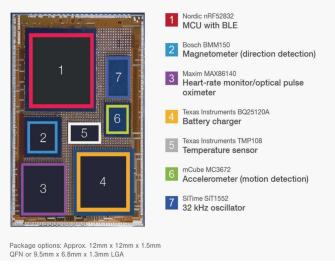

### CDX Reference design power analysis

#### Power data in datasheet

- Can it be converted to machine readable format?

- Can it be understood by tools?

#### System model?

#### Scenario definition

- Choose 2 application scenarios

#### Power analysis

Power and energy

Full analysis results <u>here</u> (see May 8, 2020 links) or <u>here</u>

#### **OmniChip Reference Design**

zGlue

zGlue Confidential and Proprietary

1

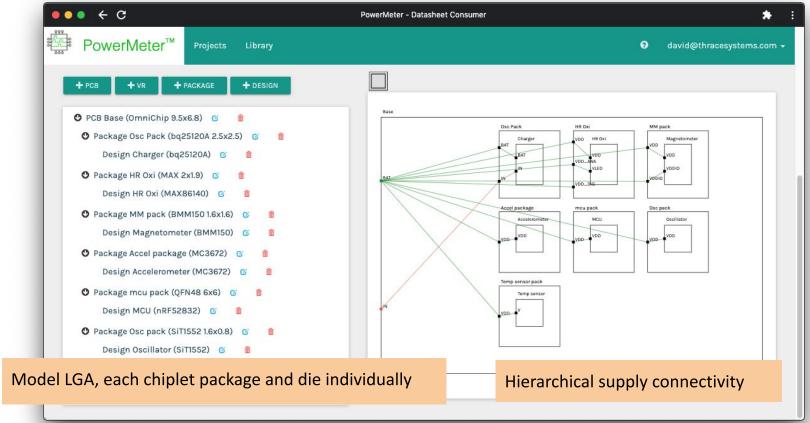

### CDX Example System: Setup Overview

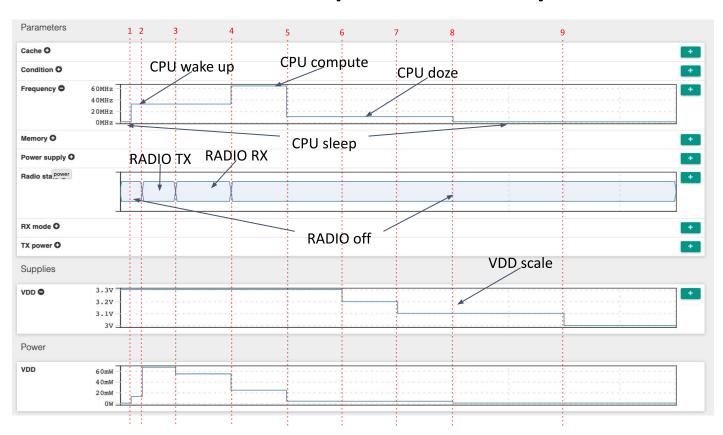

### MCU Scenario definition and power analysis

- 1. CPU wake up for processing

- 2. Begin TX

- 3. TX done, begin RX

- 4. RX done, compute result

- 5. Doze

- 6. Lower voltage

- Lower voltage again

- 8. CPU sleep

- Lower voltage again

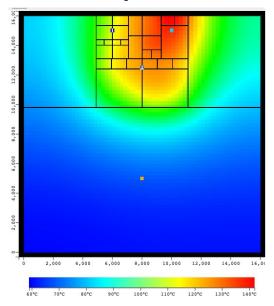

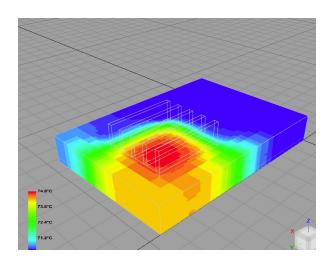

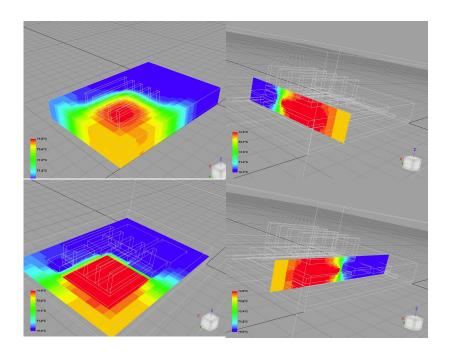

### Die & System Collaborative Thermal Analysis

High resolution Die level temperature analysis (sub-10um) Performed by SoC/Chiplet designers Uses simplified System Environment Model High resolution System level temperature analysis Performed by System designers Uses System Power Model generated by SoC designers

### Thermal analysis with ECXML

Concurrent analysis of Test-based Scenarios and Systems

Quickly iterate different options

#### Explore heat dissipation paths

|            | ECXML1 | ECXML2   | ECXML3   |  |

|------------|--------|----------|----------|--|

| Scenario 1 | 1W@35C |          | 2W@50C   |  |

| Scenario 2 |        | 1.2W@45C | 1.3W@34C |  |

| Scenario 3 |        | 0.7W@34C |          |  |

|            |        |          |          |  |

|            |        |          |          |  |

### Summary

A System Power Model enables power analysis at a higher-level of any system

Collaborative and concurrent approach to power and thermal analysis is needed starting at the early design stages

Early test system specification and modeling is key to meeting targets

## Thank You!

## Thank you sponsors!

### **ADVANTEST**®

A **global leader** in the ATE industry with a WW installed base of over 30,000 systems

Our nanotechnology products support leading-edge semiconductor processes at the **1Xnm node**

Our diverse workforce includes **5,500 employees** from **50 countries**

**Eco-friendly policies** emphasize reduction of our carbon footprint

2018 Global Technology Leader by Thomson Reuters

60+

Innovating in the measurement arena for **60+ years**

A VLSIresearch 10 BEST supplier for 32 consecutive years

## Amkor's Differentiators

### Technology

Advanced Packaging Leadership

Engineering Services

Broad Portfolio

### Quality

QualityFIRST Culture Execution Automation

### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

# Premier Assembly Materials Designer and Manufacturer:

- Thermal Interface Materials

- Liquid Metals

- Hybrid Metal TIMs

- Heat-Spring<sup>®</sup>

- Solder Pastes, Fluxes, Preforms, Alloys, Wire, and Bars

- Semiconductor Fluxes and Pastes

- Metals and Compounds

Free technical content at your fingertips

www.indium.com/insiderseries

### **COPYRIGHT NOTICE**

This presentation in this publication was presented at **Too Hot to Test** (February 9-11, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org