# Too Hot To Test

February 9 - 11, 2021

www.meptec.org

# Correlation of Low-Power Synthesis and Test Capabilities to Silicon by EDA MEPTEC 2021

Adam Cron, Principal Engineer

#### Scan Testing is Power-Hungry

Up to 10X Peak Levels of Normal Operating Mode

#### Low-Power Design and Test

Automation in TestMAX to...

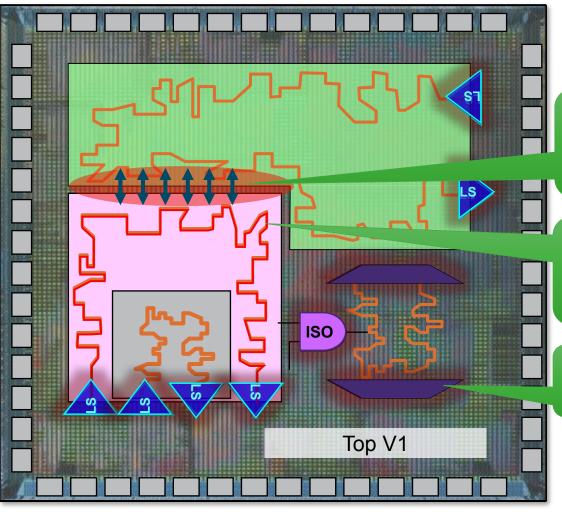

Minimize scan chain crossings between voltage domains

Ensure low-power constraints don't interfere with chain optimizations

Minimize test logic power during mission mode

# Hardware

# Shift

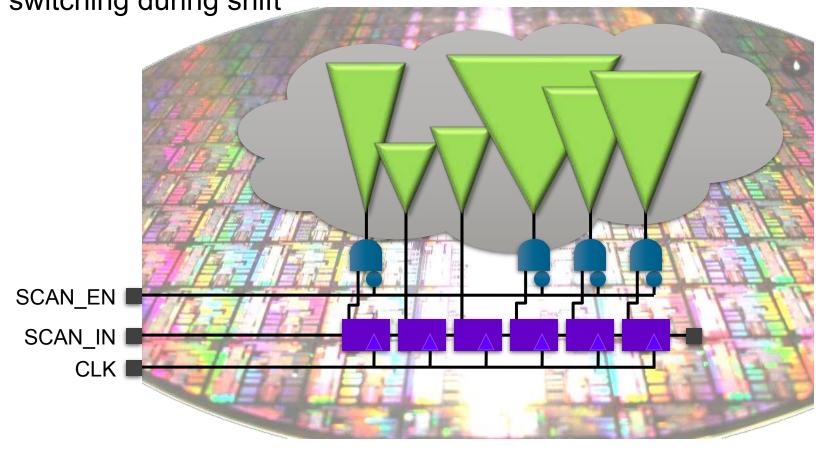

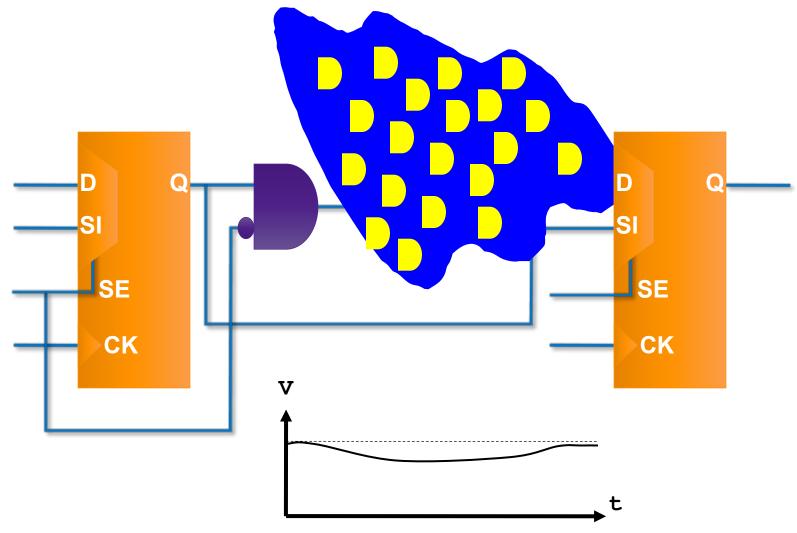

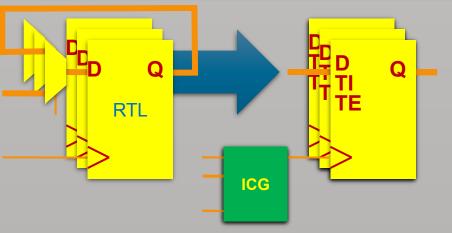

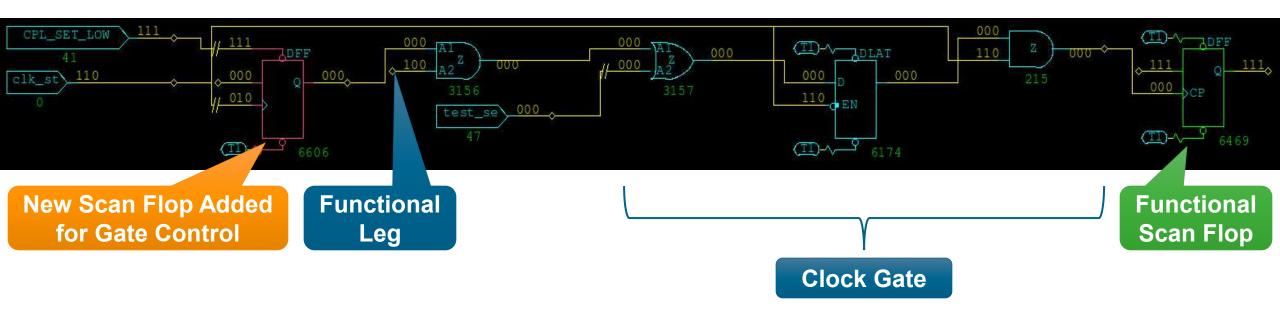

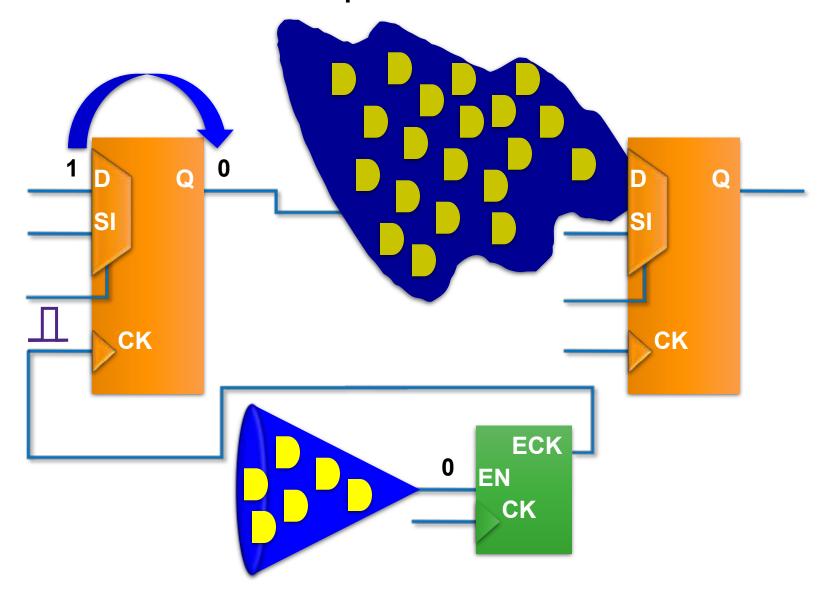

#### Q-Gating (Functional Output Gating)

- Adds a gate at the functional output of scan flop

- Logic driven by the functional output does not toggle during scan shift

Benefit: reduce power dissipation during shift

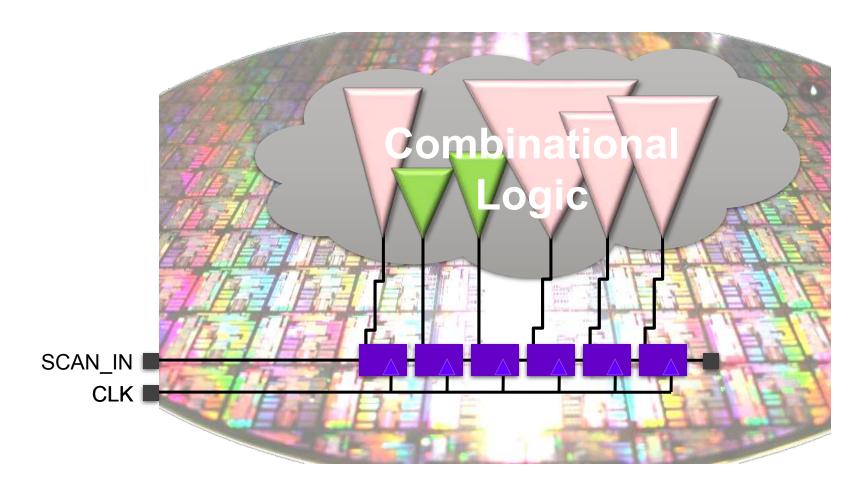

#### Shifting Produces Switching Activity in Logic Cones

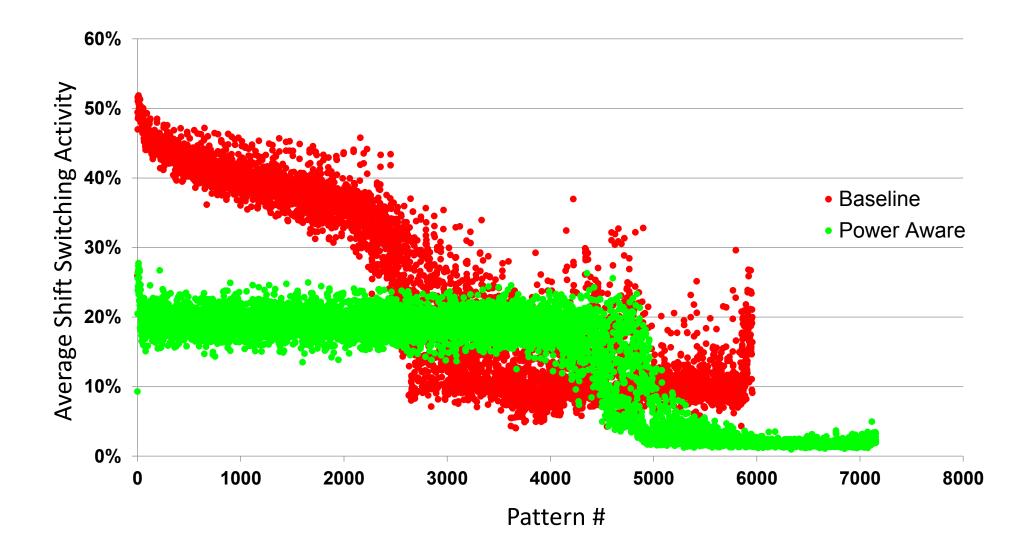

#### Power-Aware DFT

Q-gating reduces switching during shift

#### Power-Aware DFT

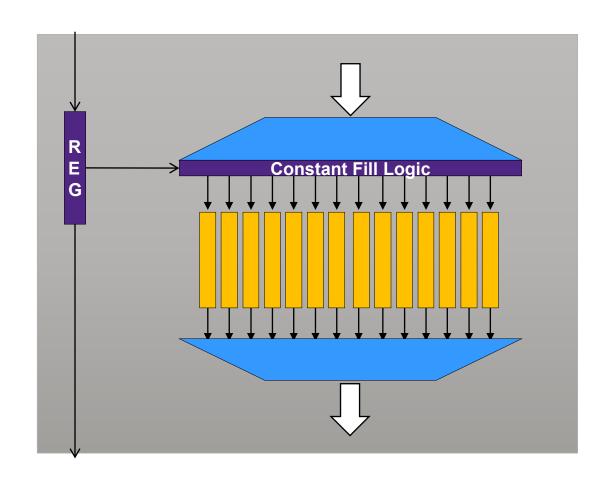

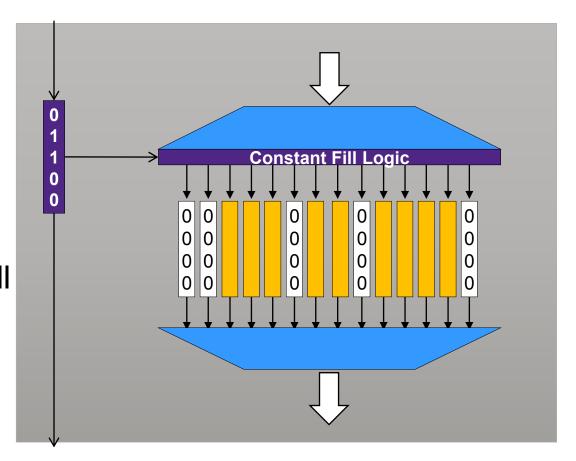

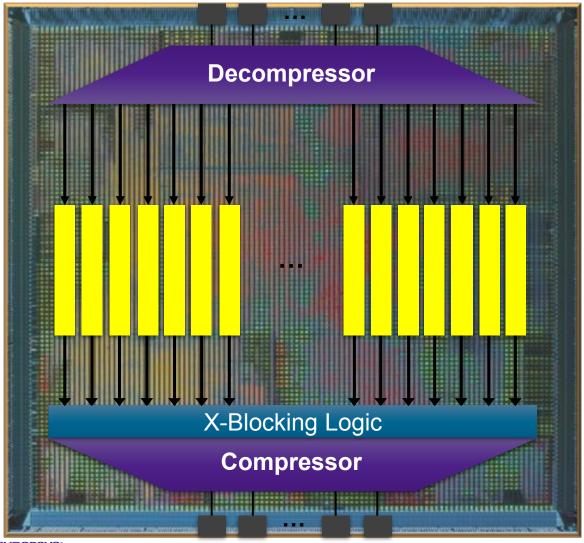

#### Reducing Shift Power for DFTMAX Compression

#### Compression codec layer

- Logic will fill scan chains with 0

- Simple combinational logic

- Register will select scan chain fill

- Dedicated scan chain, or shared with clock chain

- Register will have shift/update stage

- Stable during shift of internal chains

#### Reducing Shift Power

#### ATPG-driven selection

- User will specify peak shift toggle rate

- ATPG will use rate to determine number of zero-filled scan chains

- Each pattern will select a set of chains

- Shift power register value for pattern N will be set in pattern N-1

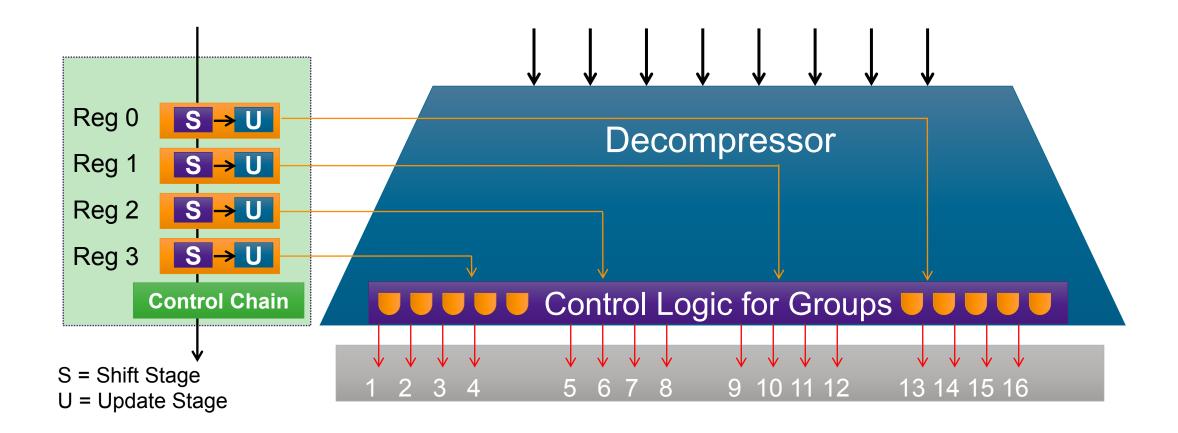

#### Control of Chain Groups

Benefit

# ATPG Only Shift Power Controller

Benefit

ATPG Only

Shift Power Controller

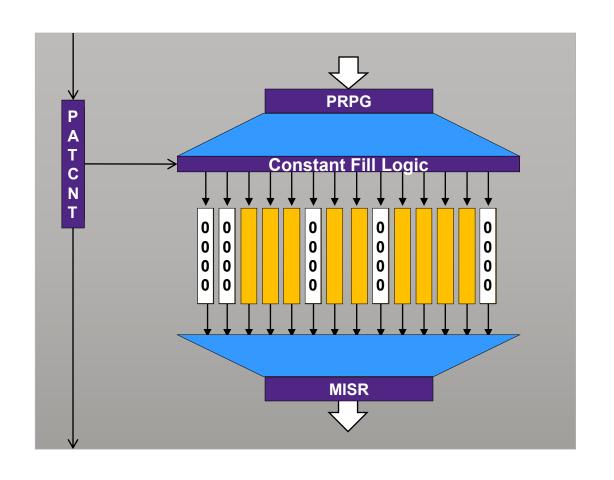

#### In-System DFTMAX LogicBIST Shift Power Control

- Logic fills scan chains with 0

- Simple combinational logic

- Pattern Counter selects scan chain fill

- DFTMAX LogicBIST

```

set_logicbist_configuration \

-shift_power_groups true \

-num_shift_power_groups N

```

TetraMAX ATPG

```

set_atpg -seq_comp_shift_power N

```

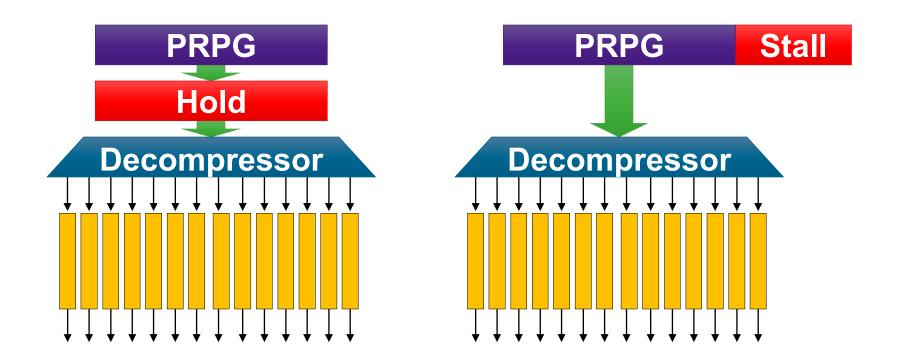

#### Low-Power Shift Mechanisms for Pseudo-Random Data Sources

- In-System LogicBIST might use other mechanisms to hold data

- DFT compression codecs that use pseudo-random pattern sources can use hold or stall mechanisms to stop PRPG data changes between shift-clock cycles

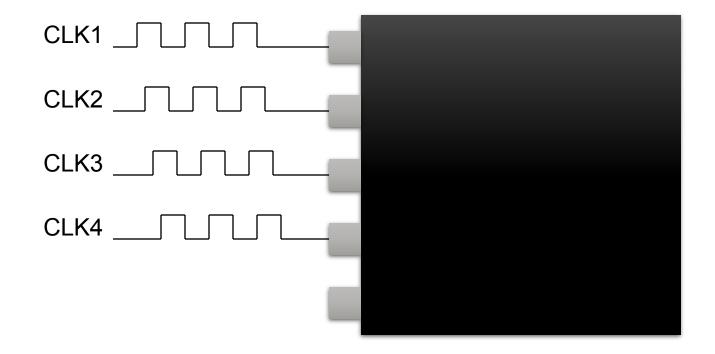

#### External Shift Clock Skewing

Adjust external clocking during shift so that multiple shift clocks do not overlap

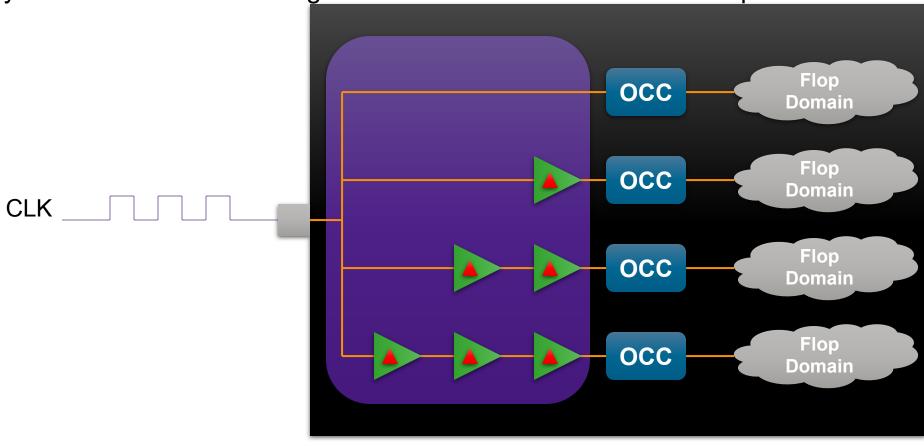

#### Internal Shift Clock Skewing Delay-Based

Add delays in shift clock so that edges in various domains do not overlap

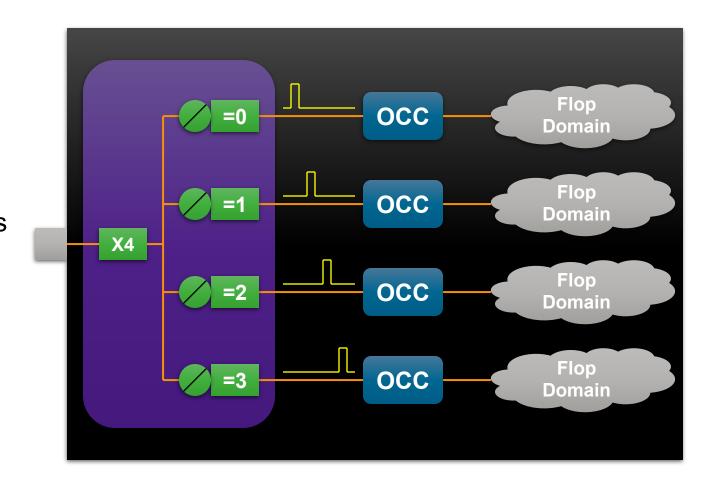

#### Internal Shift Clock Skewing Register Based

- Multiply up and down the external clock

- Pick out-of-phase clocks to drive various domains

- Use buffer for ATPG model

- Easily performed on designs using serialization and deserialization in the scan path data delivery infrastructure

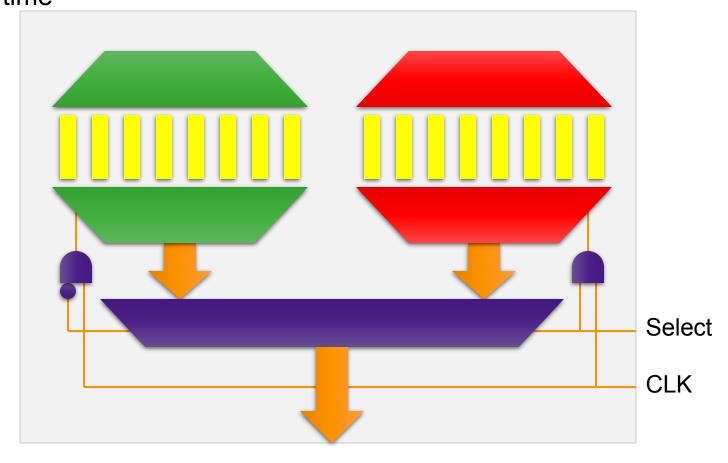

#### Multiplexed load\_unload

• Add DFT to control clocks such that all blocks do not shift at the same time (shift groups), but all capture at the same time

#### External Shift Clock Frequency Modulation

- (Based on AMD presentation at SWDFT and ITC 2014)

- Find a large voltage drop at the start of shift and adjust frequency to remove large drop

- Then speed up frequency again after some number of shifts have completed

- The following slides were inspired by:

# MITIGATING VOLTAGE DROOP DURING SCAN WITH VARIABLE SHIFT FREQUENCY

JOHN SCHULZE AMD, INC. 8 MAY 2014

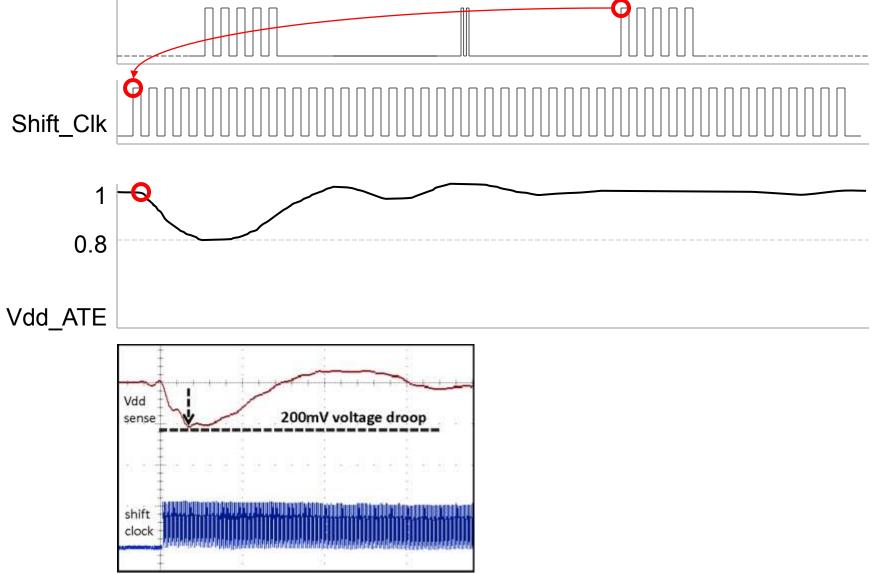

# Large Voltage Droop During Shift

Source: SWDFT, "Mitigating Voltage Droop During Scan with Variable Shift Frequency", J. Schulze, AMD, Ma8 8, 2014

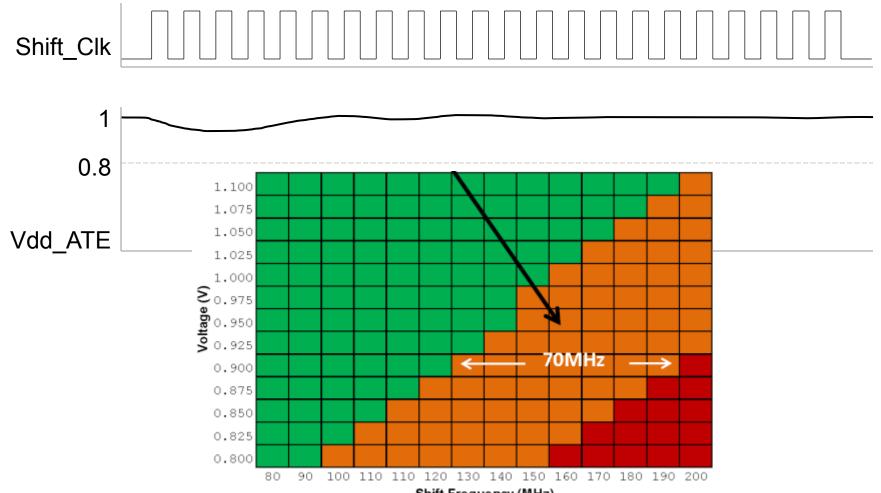

#### Slow Down Shift Clock

Shift Frequency (MHz)

Source: SWDFT, "Mitigating Voltage Droop During Scan with Variable Shift Frequency", J. Schulze, AMD, Ma8 8, 2014

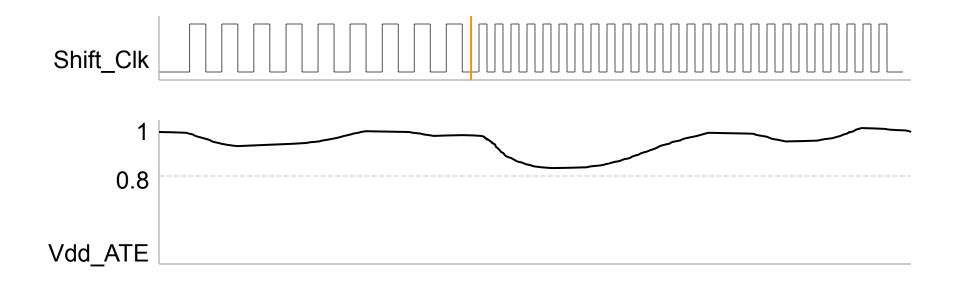

# Speed Shift Clock Up Later...

#### Find the Right Combination

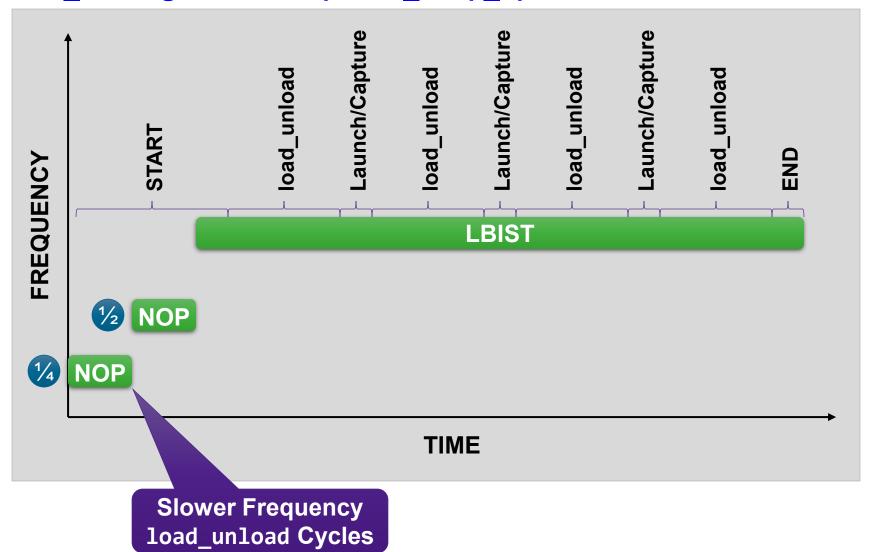

#### Shift Speed in Normal LBIST Run

set\_logicbist\_configuration -power\_ramp\_up disable

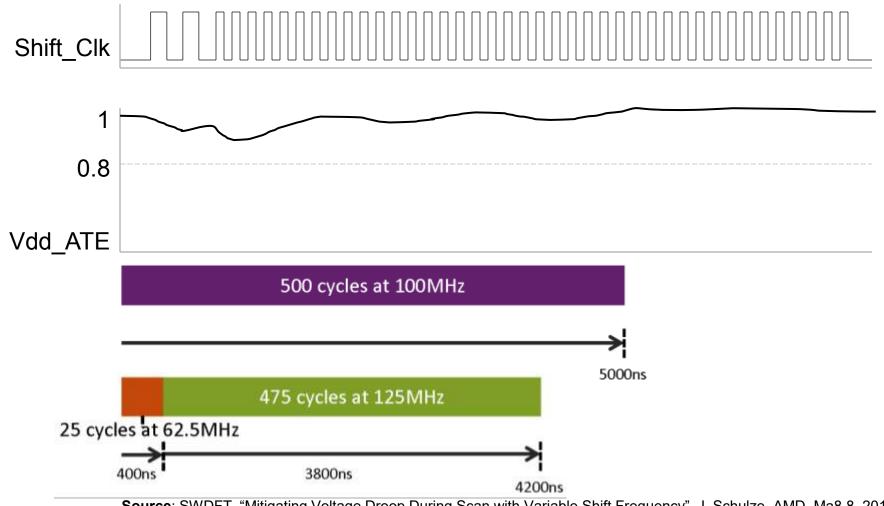

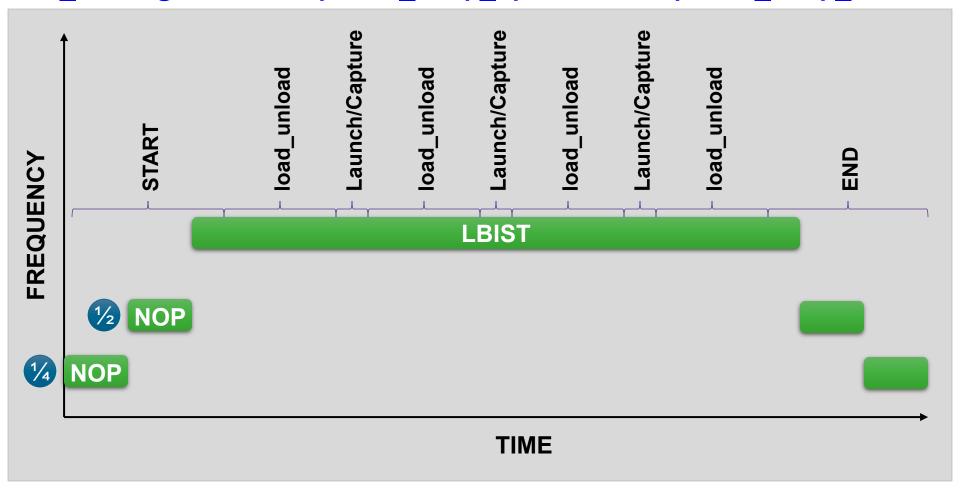

#### LogicBIST Frequency Ramp-Up

set\_logicbist\_configuration -power\_ramp\_up enable

#### LogicBIST Frequency Ramp-Up and Down

set\_logicbist\_configuration -power\_ramp\_up enable -power\_ramp\_down enable

# Capture

compile\_ultra -gate\_clock -scan

set\_dft\_configuration -scan\_compression enable

create\_test\_protocol

dft\_drc

insert\_dft

#### DFT To Limit Capture Power

When requiring a hard capture power budget (set\_atpg -power\_effort high), this feature

adds controllability resolution

set\_scan\_configuration -capture\_power\_limit N

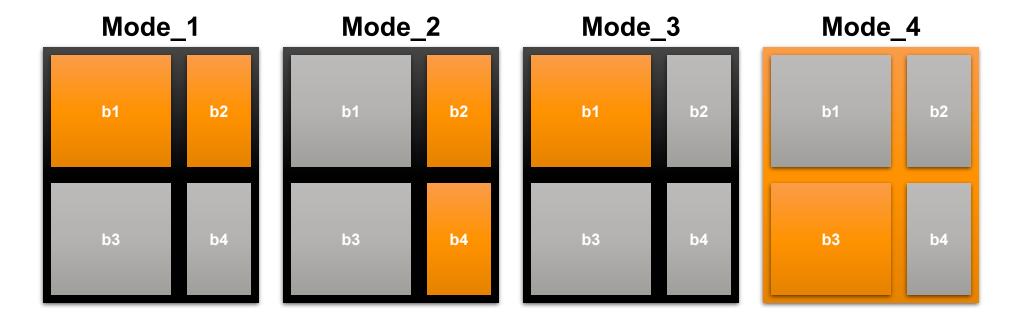

#### Block-at-a-Time

• Create more or redundant modes so that groups of modules can be tested serially, if required

#### Low-Power Compressor

- Eliminates power consumption due to switching activity in the compressor during functional mode

- Eliminates the toggling activity in the DFTMAX compressor when the XOR tree is inactive

- When SE inactive → no activity in the compressor

# **Patterns**

# Shift

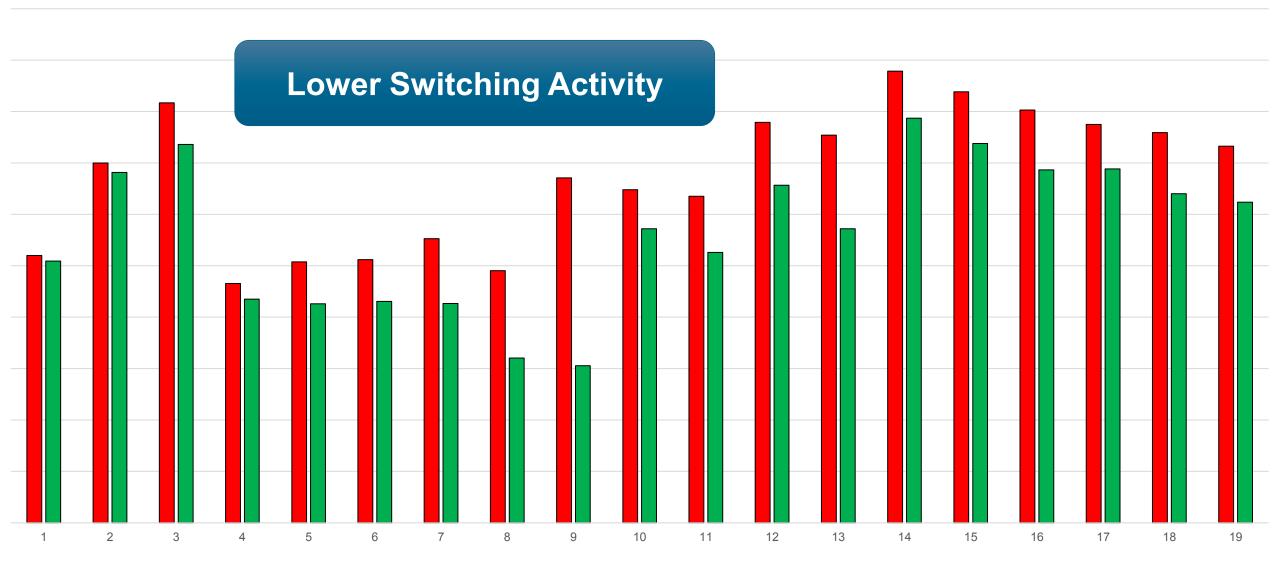

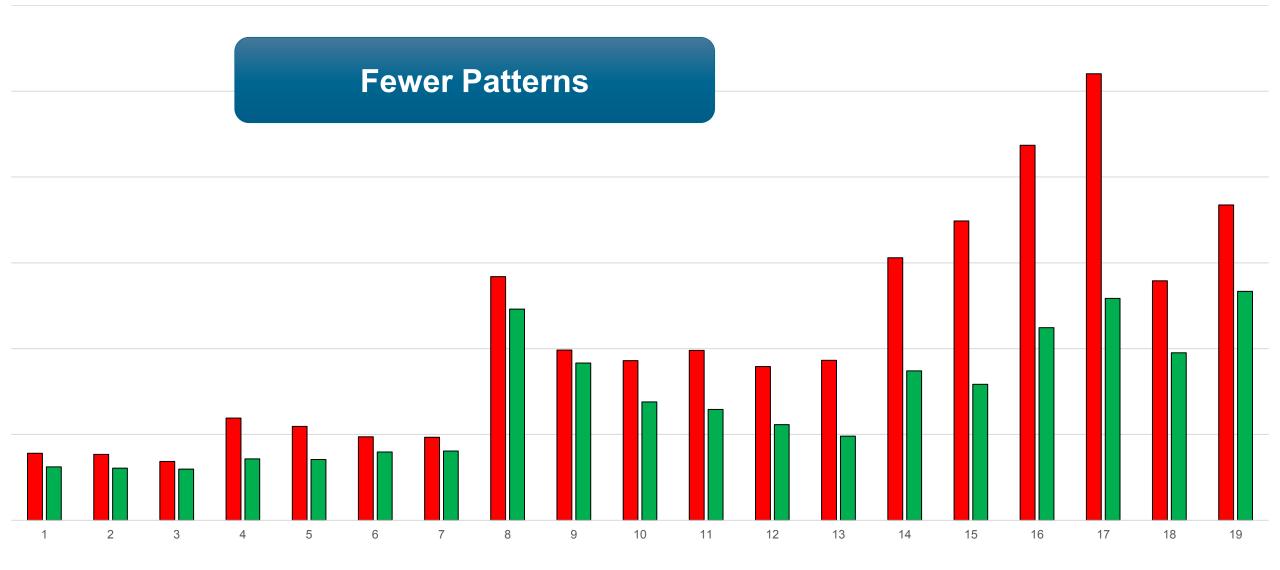

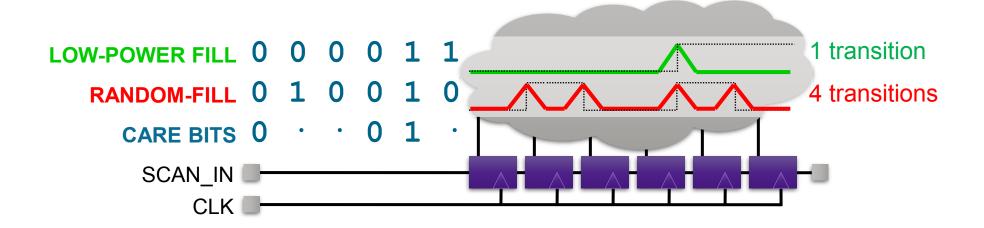

#### Low-Power Fill During ATPG to Limit Shift Power

Reduces Switching During Shift

#### **Shift Power Reduction**

# Capture

### Power-Aware ATPG for Capture Power Reduction

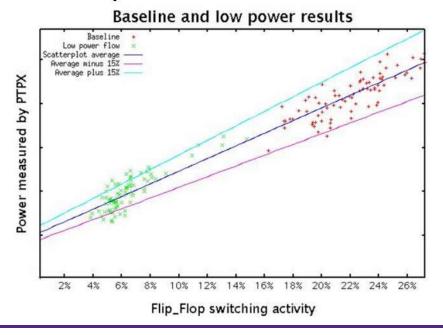

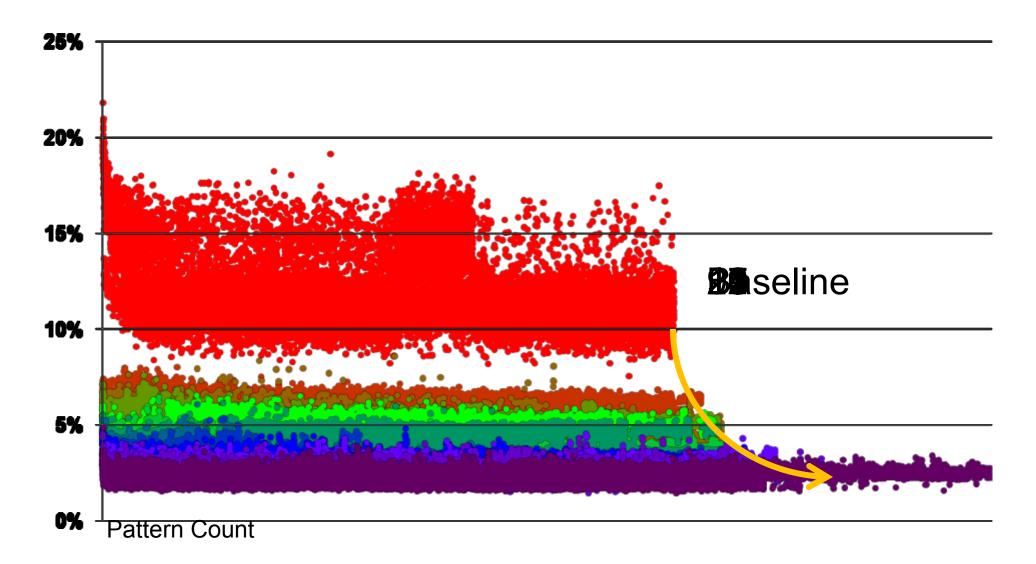

### Flop Switching and Power Correlation

#### **Peak Power Correlation**

- Overall, actual power and switching activity are closely correlated

- Majority of data points correlate within 15%

### ATPG Meets Power Budget With Fine-Grained Clock Control

- ATE clocks

- On-chip Clock Controller

- Clock Gating Cell

- Automatically meets power budget

- Avoids over-constraining ATPG

### Peak Capture Switching Percent

### Correlation

## Pre-Tapeout

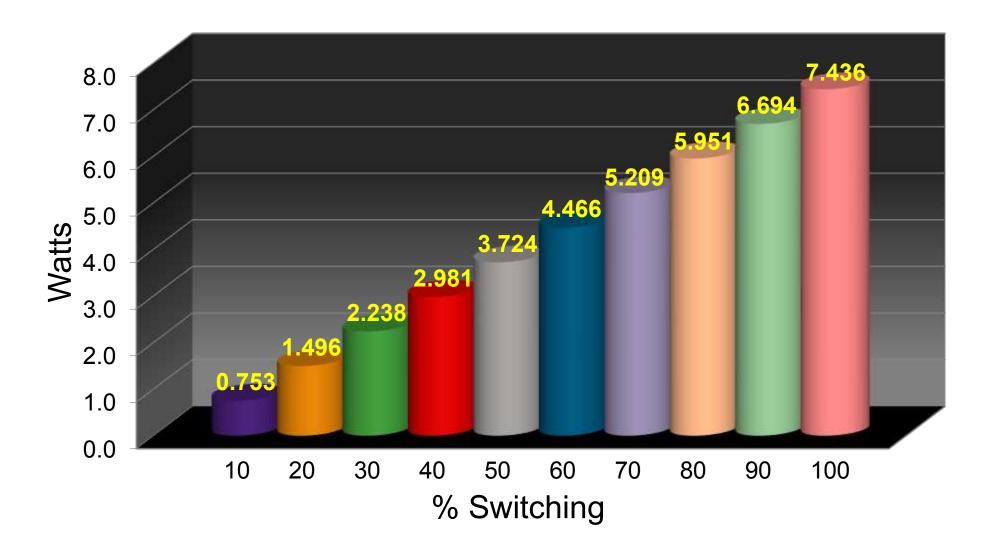

### Switching vs. Power (~10-year-old method)

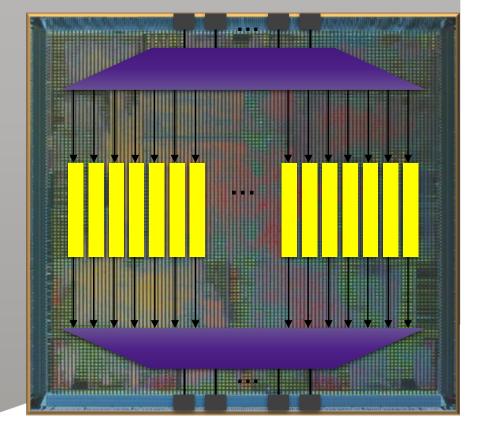

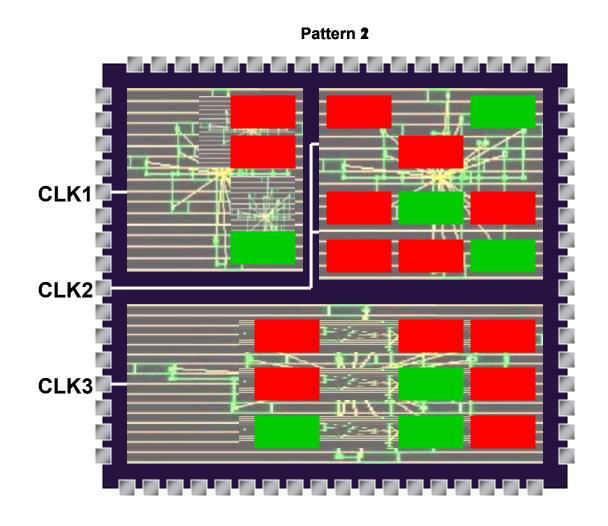

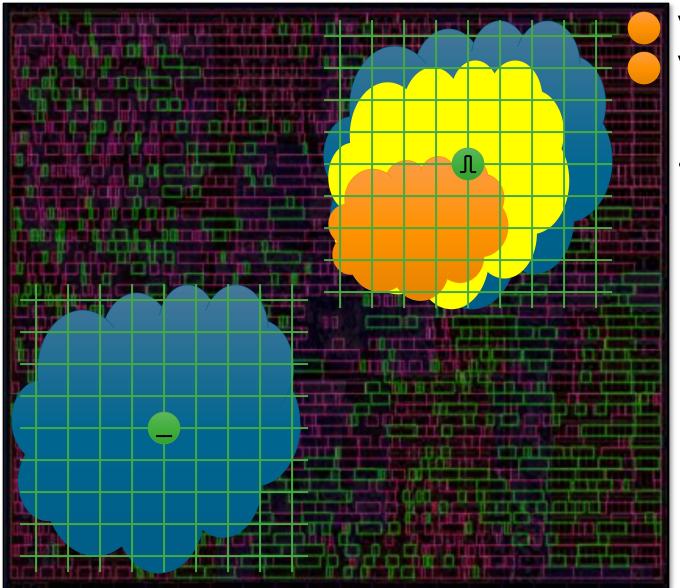

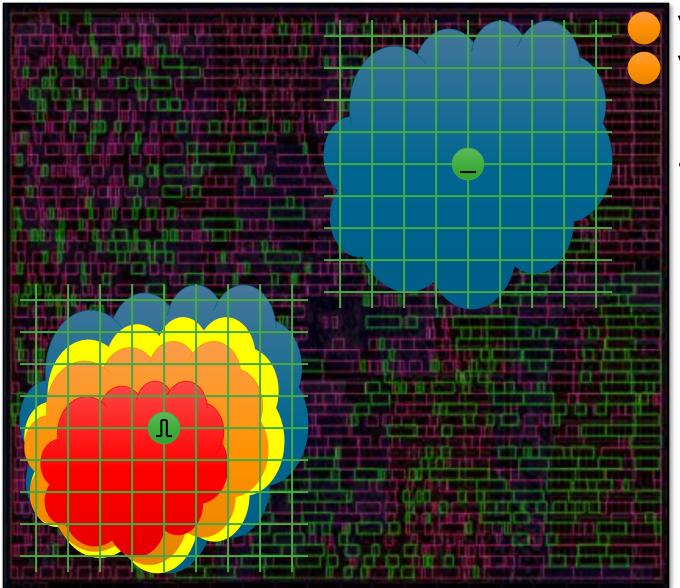

### Power Grid – For Illustration Purposes, Only

VDD VSS = OCC and Clock Mesh

- Same design in 2 places

- Same pattern set applied

### Power Grid – For Illustration Purposes, Only

VDD VSS

• IR-drop close to power source pins

### Power Grid – For Illustration Purposes, Only

VDD VSS

• IR-drop far from power source pins

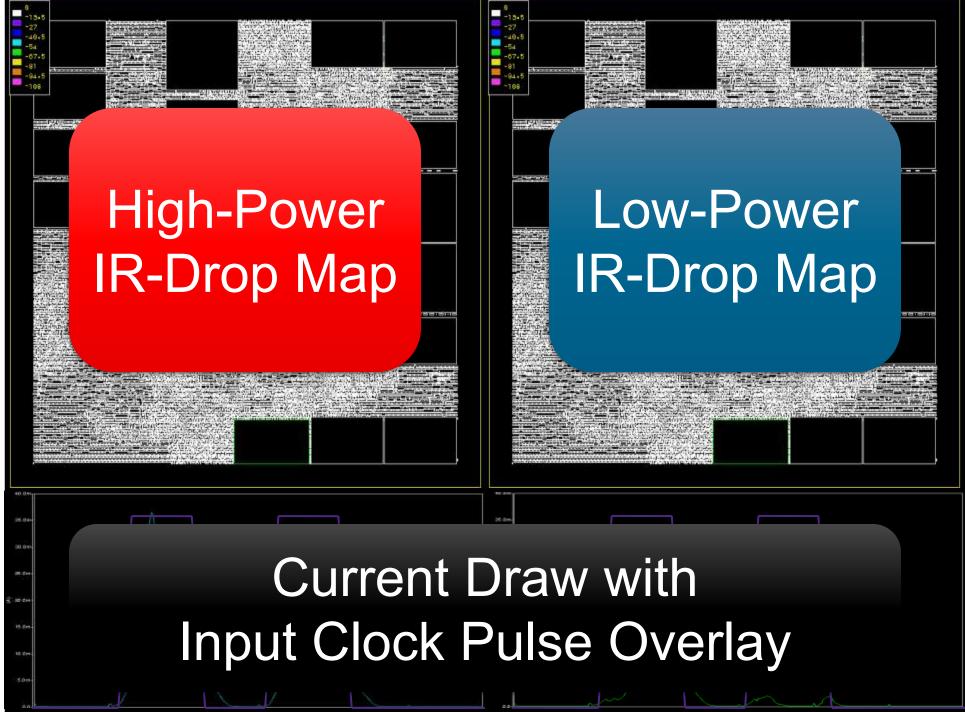

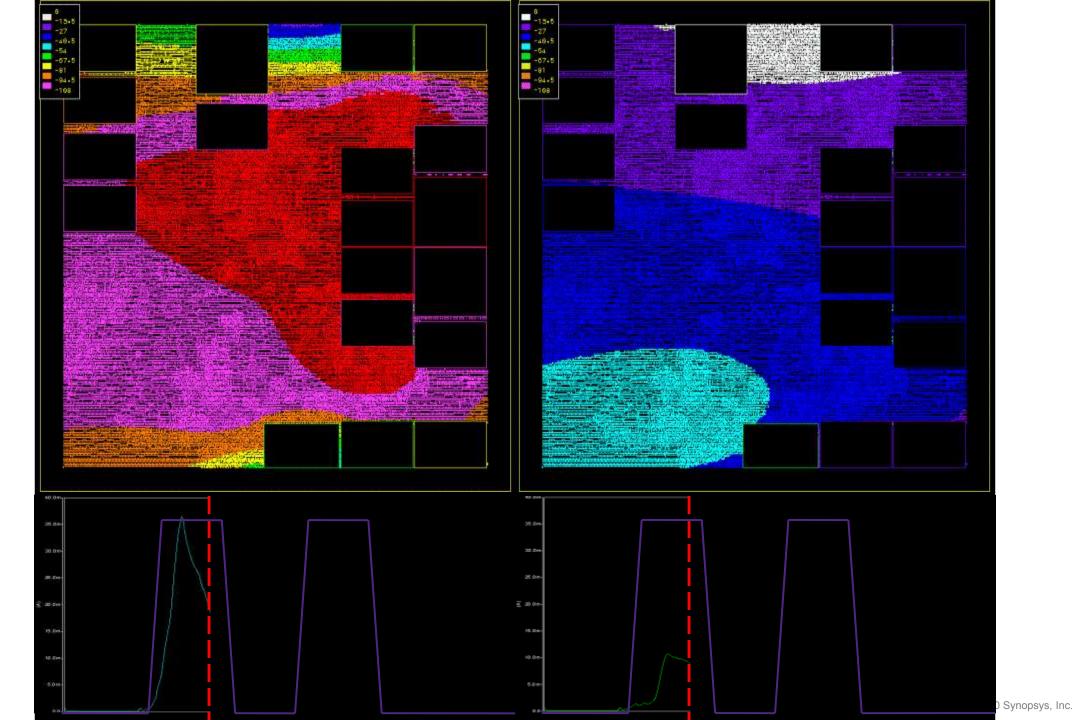

### PrimeRail Side-by-Side

PrimeTime-PX results

```

read_vcd high_power.vcd -strip AAA_tmax_testbench_1_16/dut \

-time {3500 3800}

```

### Technology Has Evolved

- Old techniques used flip-flop switching as a proxy for power

- Some tools supported combinational gates, as well

- But a correlation was still required, and reporting was only as good as the input models

- New technology uses power models to drive ATPG metrics and settings

- Flop switching, clock pulsing, combinational logic toggling, and memory accesses all drive results

- Idea is to set WATTS as a threshold, and report results in watts

## Post-Tapeout

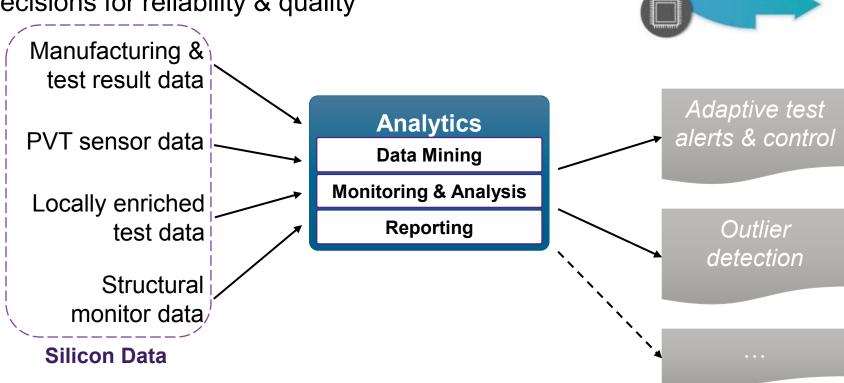

### **Test Optimization**

Test, in-chip monitoring, analytics

Adapt tests and screening criteria through ongoing analysis of silicon and manufacturing test data

Enhanced decisions for reliability & quality

**OPTIMIZE**

DATA

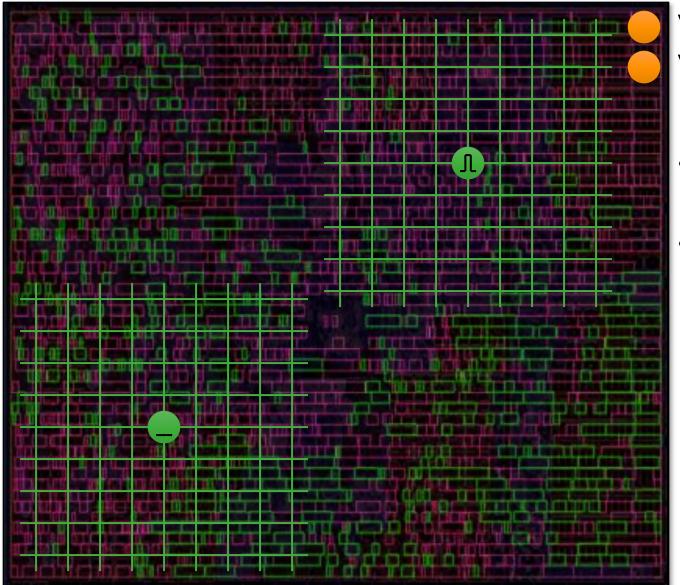

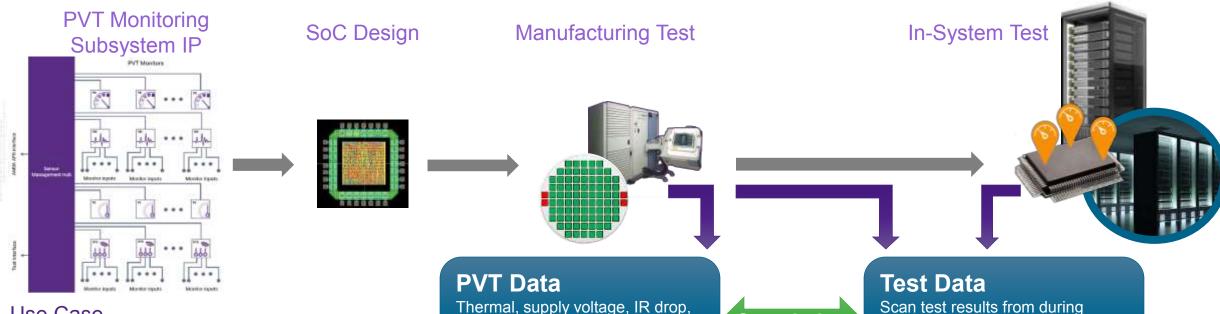

### **PVT Aware SCAN Testing**

Failing product correlated to in-chip PVT conditions

### Design

### Production

### In-field

#### Use Case

- · Assessment of SCAN data in context to physical conditions in-chip.

- · Assess thermal, supply, and speed impact of failing devices.

process spread, localized speed variation, real-time temperature during test.

Correlation

manufacturing and in-system test. Failures identified. KGD assessed.

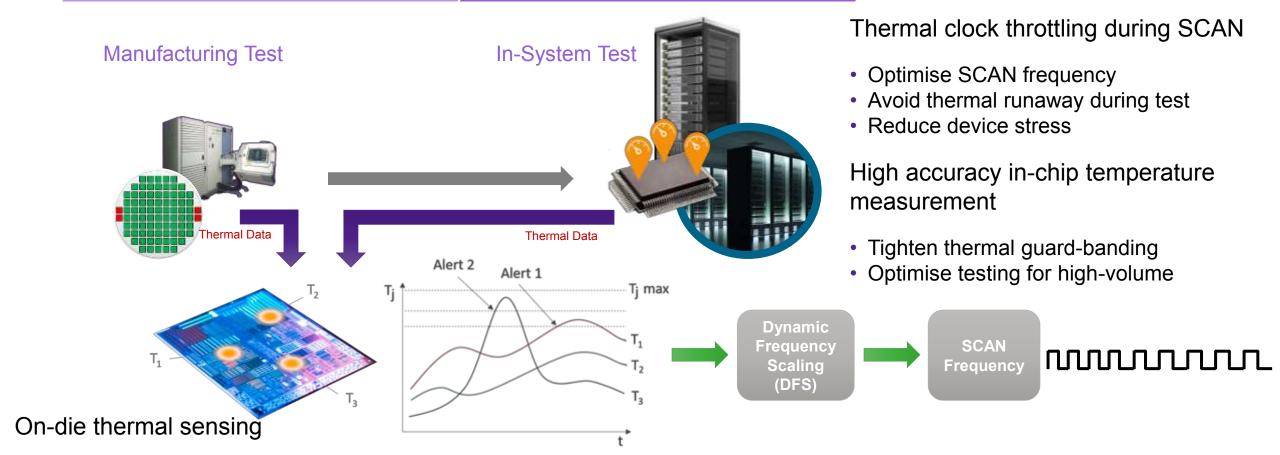

### Thermally Aware SCAN Testing

SCAN test speed modulated by in-chip temperature

### Production

### In-field

# Thank You

### Thank you sponsors!

#### **ADVANTEST**®

A **global leader** in the ATE industry with a WW installed base of over 30,000 systems

Our nanotechnology products support leading-edge semiconductor processes at the **1Xnm node**

Our diverse workforce includes **5,500 employees** from **50 countries**

**Eco-friendly policies** emphasize reduction of our carbon footprint

2018 Global Technology Leader by Thomson Reuters

60+

Innovating in the measurement arena for **60+ years**

A VLSIresearch 10 BEST supplier for 32 consecutive years

### Amkor's Differentiators

#### Technology

Advanced Packaging Leadership

Engineering Services

Broad Portfolio

### Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

# Premier Assembly Materials Designer and Manufacturer:

- Thermal Interface Materials

- Liquid Metals

- Hybrid Metal TIMs

- Heat-Spring<sup>®</sup>

- Solder Pastes, Fluxes, Preforms, Alloys, Wire, and Bars

- Semiconductor Fluxes and Pastes

- Metals and Compounds

Free technical content at your fingertips

www.indium.com/insiderseries

### **COPYRIGHT NOTICE**

This presentation in this publication was presented at **Too Hot to Test** (February 9-11, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org