## Too Hot To Test

February 9 - 11, 2021

www.meptec.org

# Our Best-Known Methods for the Testing of High-Power ICs

Dave Armstrong (dave.armstrong@Advantest.com)

### Who is Dave Armstrong?

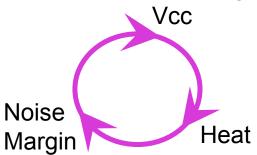

Reduced on-die V drops Improved noise margin Allowed Vee supply to reduce

→ Allowed less cooling

#### The Problem Statement

- 1. What power & cooling is really needed for my DUT.

- How to configure an ATE to meet this need.

- 3. How to interconnect these power sources to my DUT.

- 4. How to control & bring up my supplies.

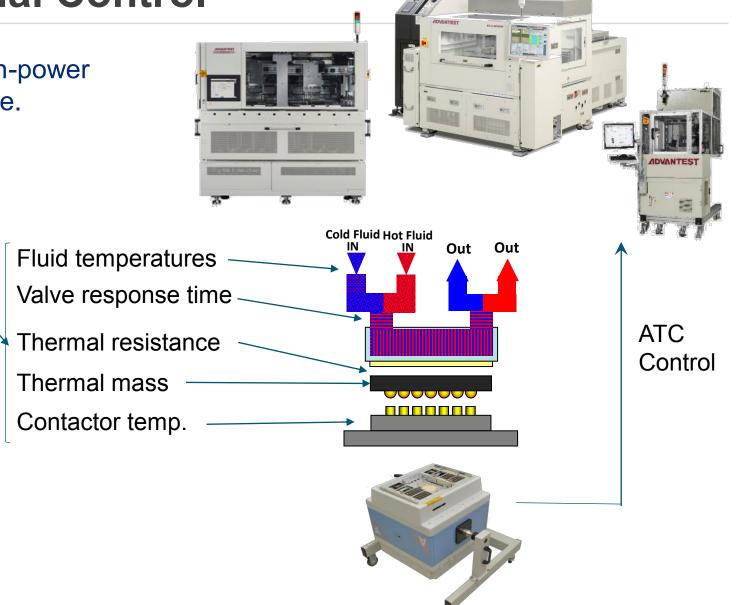

- 5. How to interface and control an Active Thermal Control system.

- 6. How to avoid burning up expensive probes.

## **How Much Power is Really Needed?**

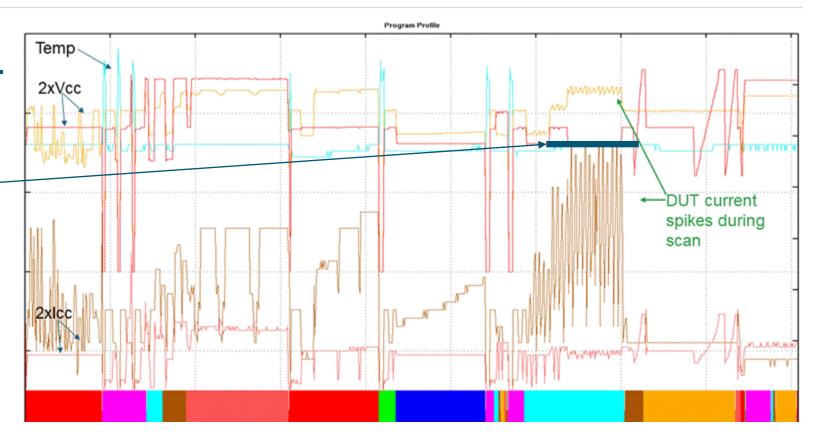

Real world data is very "messy".

The maximum current consumption is typically driven by scan test vectors.

Power aware scan pattern generation can reduce the peak current consumption significantly.

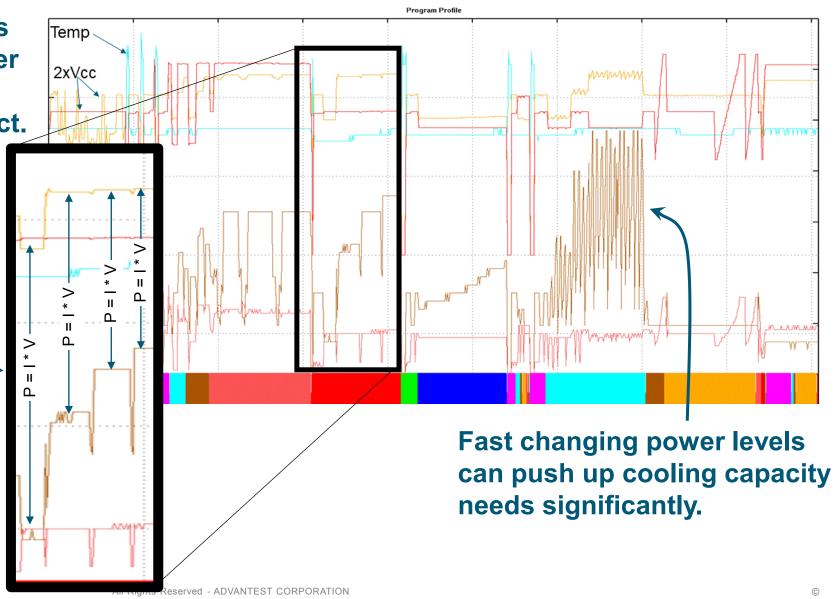

## **How Much Cooling is Really Needed?**

The cooling system capacity is designed for the average power consumption. This may be higher or lower than you expect.

First one needs to look at all the tests and calculate voltage \* current levels.

More discussion of control signals for Active Thermal Control (ATC) in later slides.

### **Ganging With Control**

#### Like a fire-hose, DPS ganging needs to avoid bottlenecks.

#### **Approach Summary for High Current Testing**

- 1. Merging in supply Module

- > Terrible approach

- > Risks cables

- > Risks probe/socket

- 2. Merging on DUT Board

- > Bad approach

- > Risks probe/socket

- 3. Merging both on chip & DUT board

- > Bad approach

- Risks probe/socket& chip

- 4. Merging only on chip> Best approach

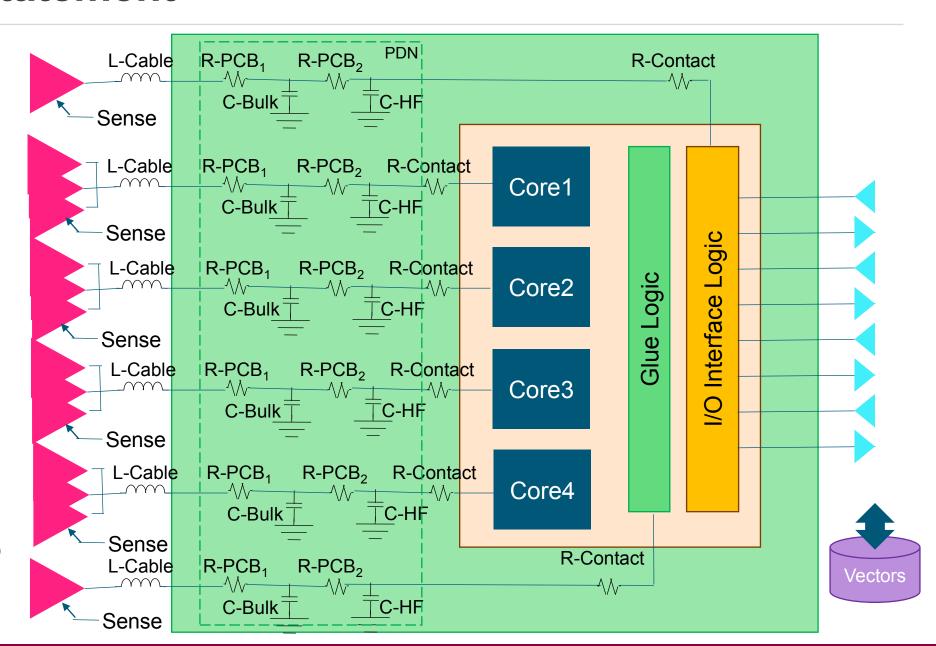

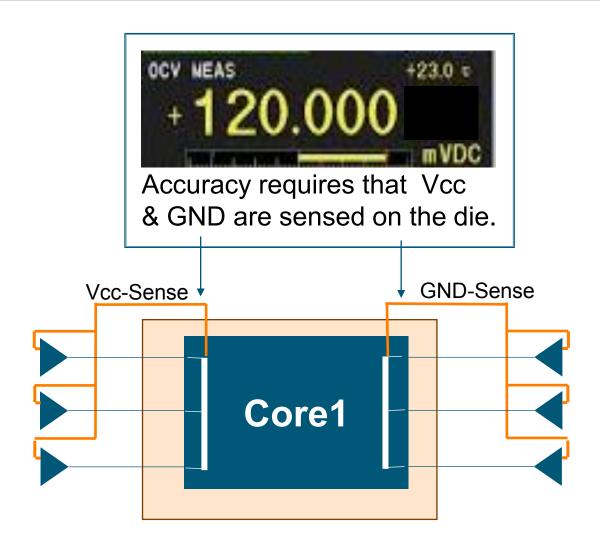

### **Accurate Sensing**

- Power supply voltage are dropping <1V. → Voltage accuracy is critical.

- Dividing up powers and ground keeps current paths clear, and noise compartmentalized.

- Having separate supplies allows better control and lower noise levels.

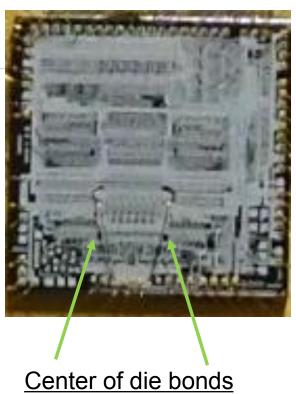

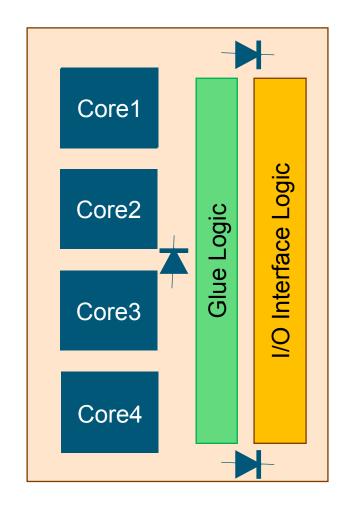

- Ground and supply sensing should be done on the device near the individual cores.

- If you have supply and/or ground paths feeding multiple cores, consider switching to different sense lines as different cores are being tested.

## **Avoiding Burnt Probes** – (1st of 3 Key Tasks)

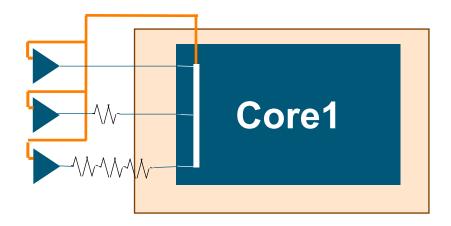

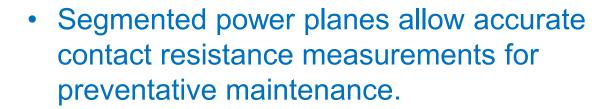

#### Burnt probe cards is a major cost factor to the industry

1. Ensure that probe current is well controlled

- Active current balancing between the parallel channels avoids exceeding CCC.

- If contact resistance becomes too high on one of the channels current can be redistributed within design constraints. If excessive an alarm can be raised.

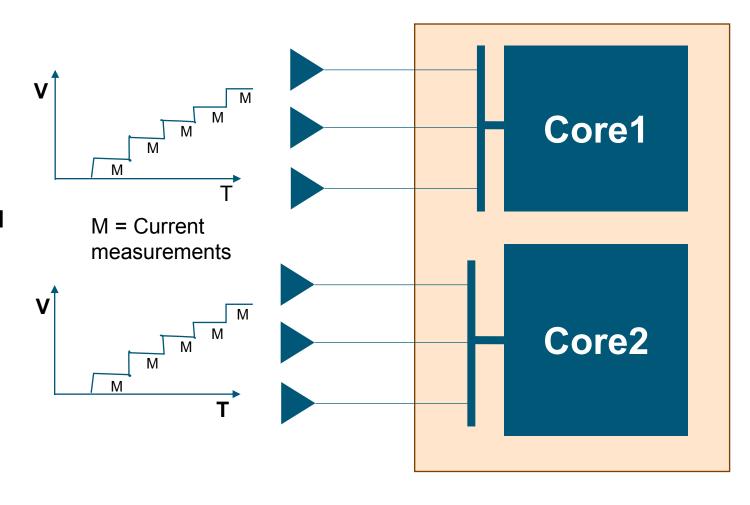

## Turn Supplies on Carefully & Check Currents (2nd of 3 key tasks)

# 2. Turning on high-current supplies must be done very carefully.

- Since shorts can occur between power and ground as well as between cores, multiple cores with separate supplies must be powered up in lock-step.

- Using a small voltage step (typically <100mV) gives time for everything to settle.

- Checking the current draw after each step allows sequence to stop if a problem is noted.

#### **Avoiding Burnt Probes** (3rd of 3 Key Tasks)

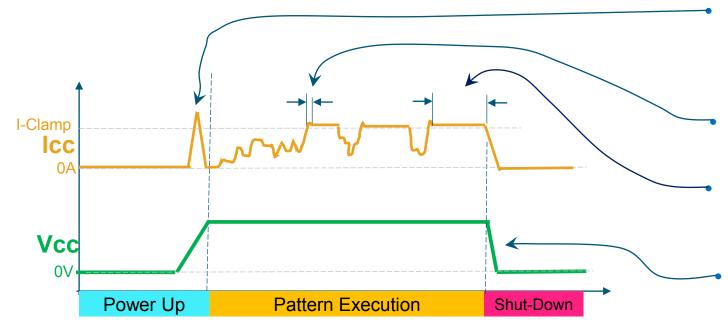

#### 3. Respond in a fast and well-controlled way.

Current influx during capacitor charge must be controlled and understood to avoid problems.

Fast clamp response time (< 200us).

Programmable fold-back time triggers shut down multiple supplies on a per-site basis.

DPS needs to quickly discharge bulk capacitors to avoid arching when probe lifted.

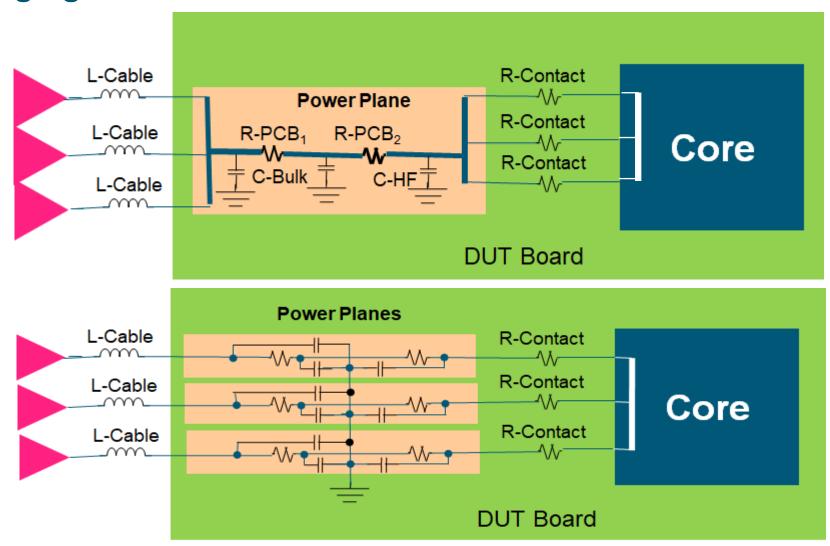

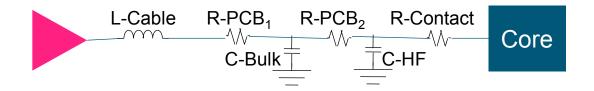

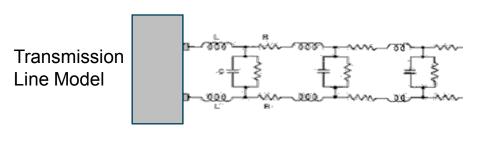

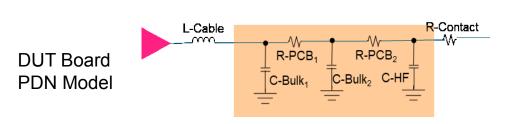

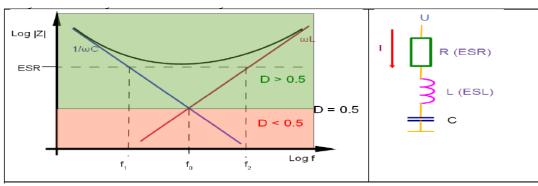

#### **Power Distribution Networks**

#### The DUT board circuitry is very similar to a transmission line.

When designing a DUT board selecting the right capacitors in the right quantity is critical. "Too Little" C is certainly bad . . . And "Too Much" C can also be worse.

#### The next challenge is DUT board area & component costs.

- All high-power DUT-Boards need the right amount of tantalum bulk capacitance for optimal droop performance.

- All DUT-boards need good high-BW ceramic bypass capacitors near the DUT.

- Tantalum capacitors provide superior value for bulk-C:

- ✓ Pros: Wider temperature range Higher uF/mm² Lower \$\$/uF

- Cons: Higher ESR @ High F Polarized

#### The Art of Active Thermal Control

Advantest has very fast responding high-power handlers and a die-level prober available.

Fundamental constraints limit the response time to milliseconds.

The ATC control signal is key to avoiding over and under temp conditions. Three methods are available:

- 1. Thermal diodes

- 2. Power Following

- 3. Power Anticipating

#### **ATC Interfaces – Thermal Diodes**

Adding a thermal diode into the chip is quite standard today.

**Single** diode feedback is inadequate for high-power designs as different areas of the die heat up with different amounts at different times.

-----

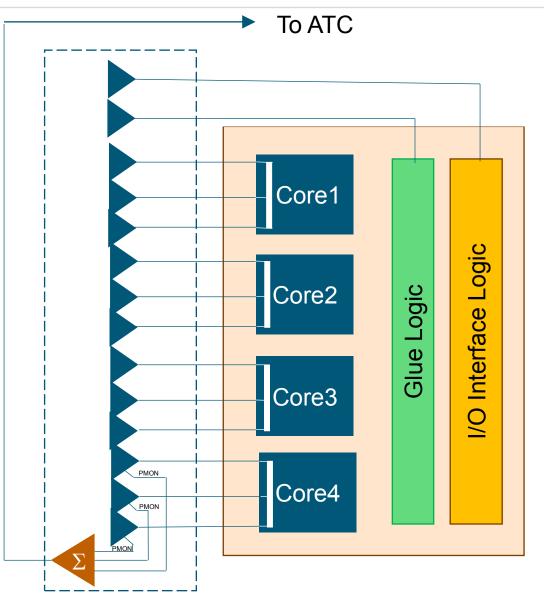

**Multiple** diode feedback is strongly recommended for high-power device testing. These signals can be combined in different ways: Max temp, average temp, targeted/switched temp to name a few.

## **ATC Interface – Power Following**

Supply <u>current</u> feedback has been used for years in "Power Following" applications.

Best case this gave the ATC system a few microsecond head-start and feedback was only current not power.

New ATE power supplies can send a tracking signals proportional to actual <u>power</u> consumption out to the thermal control system.

This allows the ATC response to be focused by the test flow on the core(s) active in the test at that time.

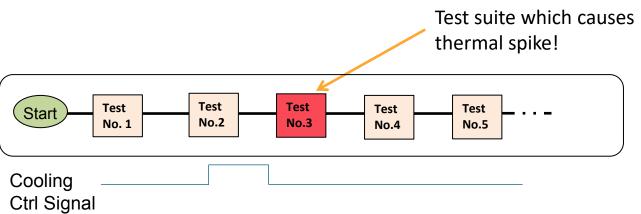

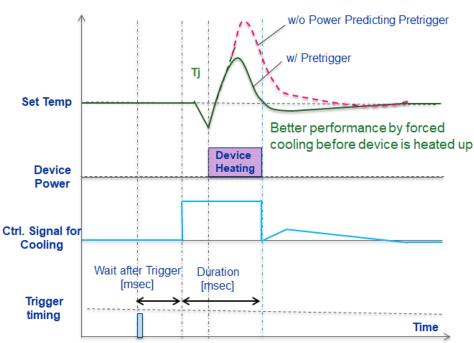

## **ATC Interface – Power Predicting**

The test system knows when more cooling is going to be needed.

The V93K can send the ATC system a pre-trigger so that temperature extremes are avoided.

(19) United States

(12) Patent Application Publication

ARMSTRONG et al.

(19) Pub. No.: US 2014/0253155 A1

(20) Pub. Date: Sep. 11, 2014

(24) ADAPTIVE THERMAL CONTROL.

(27) Avaignet: Advantest Curperation, Takyo (P)

(28) Inventor: David IL AUNSTRONG, Lidgotte (ISS, Mile CALLAWY, La Mono, CA

(105)

(29) Avaignet: Advantest Curperation, Takyo (P)

(21) Appl. No.: 1419-955

(21) Fibel: Man. 4, 2014

Related US. Application Data

(26) Persistent application No. 81774-500, fibed on Mar. 7, 2013.

Publication Classification

(27) Data (ISS) (ISS)

Advantest Patent #9291667

### BKM's for High-Power Device Testing

#### Plan Ahead!

- Select the right ATE, handler, prober, probes, contactors, and thermal control systems.

- Calculate maximum current draw considering scan patterns plans & power-aware EDA tools to config ATE.

- Work with cooling system experts to size capacity based on Vmax\*Imax\*DC + uplift for fast power changes.

#### **DUT Boards need lots of attention!**

- Use tantalum bulk capacitors of the right  $C_{total}$  per the calculator.

- Use good high-frequency ceramic capacitors near the DUT.

- Each high-consuming sub-circuit (core) likely needs its own supply current path as well as sense feedback.

- If you have extra DPS channels gang them with your highest current channels for faster settling times.

- Explore possible usage of high current-carrying probes or pogos.

#### Careful test programming is critical! 3.

- Slowly step the various core voltages up while monitoring the current draws for any problems.

- Utilize power-aware EDA tools to create patterns which minimize high-power transients.

- Space out your high-power events to minimize average power dissipation.

## Thank you sponsors!

#### **ADVANTEST**®

A **global leader** in the ATE industry with a WW installed base of over 30,000 systems

Our nanotechnology products support leading-edge semiconductor processes at the **1Xnm node**

Our diverse workforce includes **5,500 employees** from **50 countries**

**Eco-friendly policies** emphasize reduction of our carbon footprint

2018 Global Technology Leader by Thomson Reuters

60+

Innovating in the measurement arena for **60+ years**

A VLSIresearch 10 BEST supplier for 32 consecutive years

## Amkor's Differentiators

#### Technology

Advanced Packaging Leadership

Engineering Services

Broad Portfolio

#### Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

# Premier Assembly Materials Designer and Manufacturer:

- Thermal Interface Materials

- Liquid Metals

- Hybrid Metal TIMs

- Heat-Spring<sup>®</sup>

- Solder Pastes, Fluxes, Preforms, Alloys, Wire, and Bars

- Semiconductor Fluxes and Pastes

- Metals and Compounds

Free technical content at your fingertips

www.indium.com/insiderseries

#### **COPYRIGHT NOTICE**

This presentation in this publication was presented at **Too Hot to Test** (February 9-11, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org