# Too Hot To Test

February 9 - 11, 2021

www.meptec.org

#### **TERADYNE**

Optimizing Test Based on Device Temperature

#### What's the Problem?

- Devices heat up the faster you try to test them, especially during structural test

- Packaging is usually designed for mission (application) mode, where temperatures are lower

- Test done at wafer probe has no package to conduct away heat

- Device behavior changes with variations in temperature

#### This costs money

- Minor problem: test time goes up, meaning more equipment time is required to adequately test the device

- Major problem: Thermal issues may cause device overkill (throwing away good devices)

- Today there are only crude solutions to this

- Monitor case (package) temperatures

- Slow down testing until it works

- Can you monitor die temperature?

- Not in ways that are really useful

## A few things about "Cost of Test"

- If someone could increase yield by 5% by doubling their test time, they would do it happily

- Test isn't that expensive compared to silicon costs

- A lot of time is spent fixing the device, not "testing" it

- Vdd trim, memory repair, harvesting partially working devices

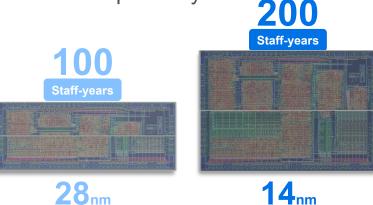

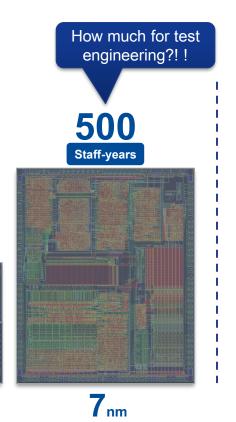

- It takes a lot of effort to generate a test program and there is a lot of time pressure

- It is the last thing that needs to happen before a device can be shipped.

100,000 lines of code that must work perfectly

**Empire state building**

#### The Problem of Structural Test

- Structural test is designed explicitly to toggle as many transistors as possible to test functionality as quickly as possible

- Activity is localized with higher activity levels

- Structural test is an "un-natural" mode of operation for the device

- Consumes far more power

- Generates far more heat

- Only used during test, so packaging is not optimized for this case

- What can we do today?

- We can speed up or slow down shift rates

- We can re-order tests

- We can add cooling to IC handlers and prober chucks, which is expensive and imprecise

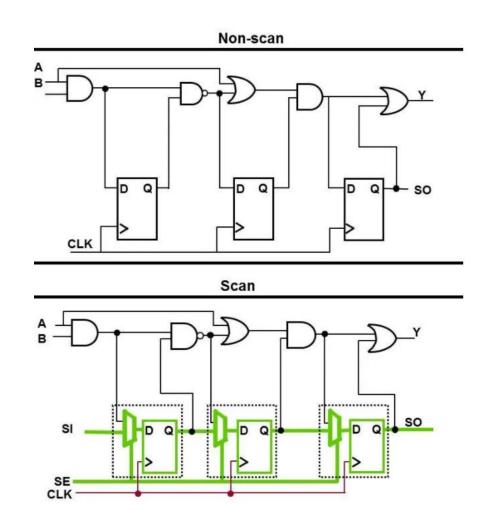

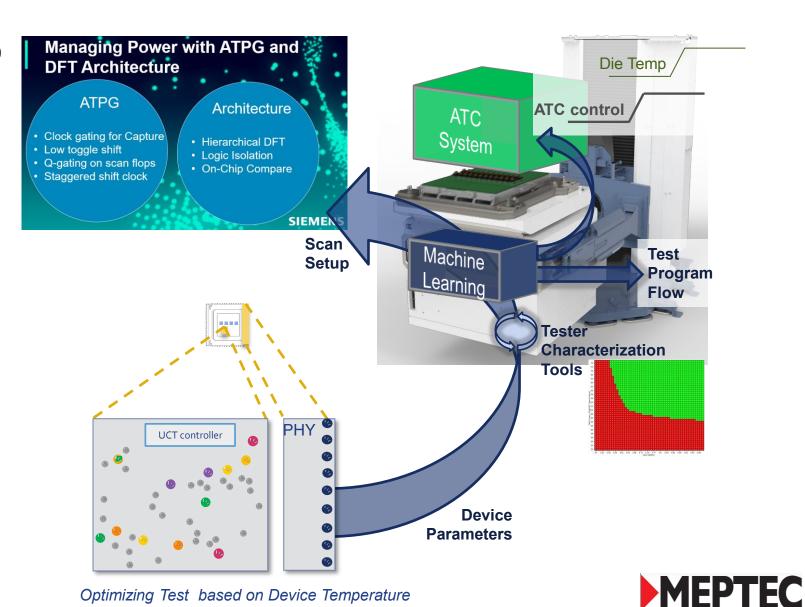

# New Scan Structures Reduce Overall Cycle Count

Managing Power with ATPG and **DFT Architecture** Typical tools for power management **ATPG** Architecture Test conditions (ATPG) Device design Clock gating for Capture Hierarchical DFT Low toggle shift Logic Isolation Q-gating on scan flops On-Chip Compare Staggered shift clock **SIEMENS**

Avoiding localised Heating and Hotspots

| Managing test flow based on physical layout

| Testing Per Column | Checkerboard Testing | SIEMENS | SIEMENS | Checkerboard Testing | Checke

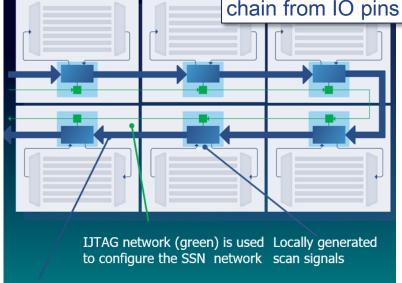

Scan "network" that reduces overhead and decouples internal scan chain from IO pins

Scan data is transmitted over an N-bit wide high speed SSN bus and delivered to EDT through a "host node" (light blue box).

J-F. <u>Côté</u>, et.al., "Streaming Scan Network (SSN): An Efficient Packetized Data Network for Testing of Complex <u>SoCs</u>," ITC 2020. **SIEMENS**

|                                           | SSN (32b bus size)         |                        |                         |                       | Pin-muxed GPI (estimated)  |                        |      |                         |      |                       |

|-------------------------------------------|----------------------------|------------------------|-------------------------|-----------------------|----------------------------|------------------------|------|-------------------------|------|-----------------------|

| Patterns                                  | Setup<br>cycles<br>(IJTAG) | Scan<br>Test<br>Cycles | Total<br>Test<br>Cycles | Total<br>Data<br>(Mb) | Setup<br>Cycles<br>(IJTAG) | Scan<br>Test<br>Cycles | /    | Total<br>Test<br>Cycles |      | Fotal<br>Data<br>(Mb) |

| 10                                        | 34,703                     | 3,280                  | 37,983                  | 0.28                  | 20,446                     | 5,740                  |      | 26,186                  |      | 0.29                  |

| 500                                       | 34,703                     | 136,120                | 170,823                 | 4.53                  | 20,446                     | 241,900                |      | 262,346                 |      | 7.74                  |

| 10000                                     | 34,703                     | 2,711,740              | 2,746,443               | 86.95                 | 20,446                     | 4,820,780              |      | 4,841,226               |      | 154.26                |

| STF vs. SSN @ 10K patterns Pinmux vs. SSN |                            |                        |                         |                       |                            | 1                      | 1.76 | 7                       | 1.77 |                       |

40% Reduction in overall test cycles to do the same amount of testing

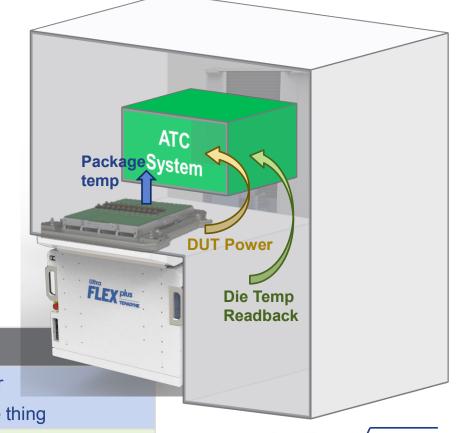

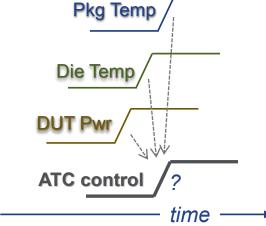

#### Automatic Temperature Control (ATC) Systems

Handler and probers can provide cooling based on feedback from the DUT or Tester, but no method is really perfect

| Method                        | Pros                                                                                                                               | Cons                                                                                              |  |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--|--|--|

| Monitor package temperature   | <ul> <li>Easy to do (self contained in handler or prober)</li> </ul>                                                               | <ul><li>Lagging (late) indicator</li><li>Can only measure one thing</li></ul>                     |  |  |  |

| Die Temperature<br>Readback   | <ul><li>Exactly what you care about</li><li>Can measure multiple physical locations</li></ul>                                      | <ul><li>Latency is too long to use in real time</li><li>No uniformity in implementation</li></ul> |  |  |  |

| Monitor Device Power Supplies | <ul><li> "Early indicator" of DUT temperature</li><li> Can get core-specific information</li><li> "Smart Control" of ATC</li></ul> | Device is probably hot before ATC is effective                                                    |  |  |  |

| All of these                  | Adaptive                                                                                                                           | Not predictive                                                                                    |  |  |  |

#### How to Make This Better?

If you want these...

You need to solve these...

| Method                           | Pros                                                                                                                           | Cons                                                                                                 |  |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|--|

| Monitor package temperature      | Easy to do (self contained in handler or prober)                                                                               | <ul><li>Lagging (ate) indicator</li><li>Can only measure one thing</li></ul>                         |  |  |  |  |

| Die Temperature<br>Readback      | <ul><li>Exactly what you care about</li><li>Can measure multiple physical locations</li></ul>                                  | <ul> <li>Latency is too long to use in real time</li> <li>No uniformity in implementation</li> </ul> |  |  |  |  |

| Monitor Device Power<br>Supplies | <ul><li>"Early indicator" of DUT temperature</li><li>Can get core-specific information</li><li>"Smart Control of ATC</li></ul> | Device is probably hot before ATC is effective                                                       |  |  |  |  |

| All of these                     | Adaptive                                                                                                                       | • Not predictive                                                                                     |  |  |  |  |

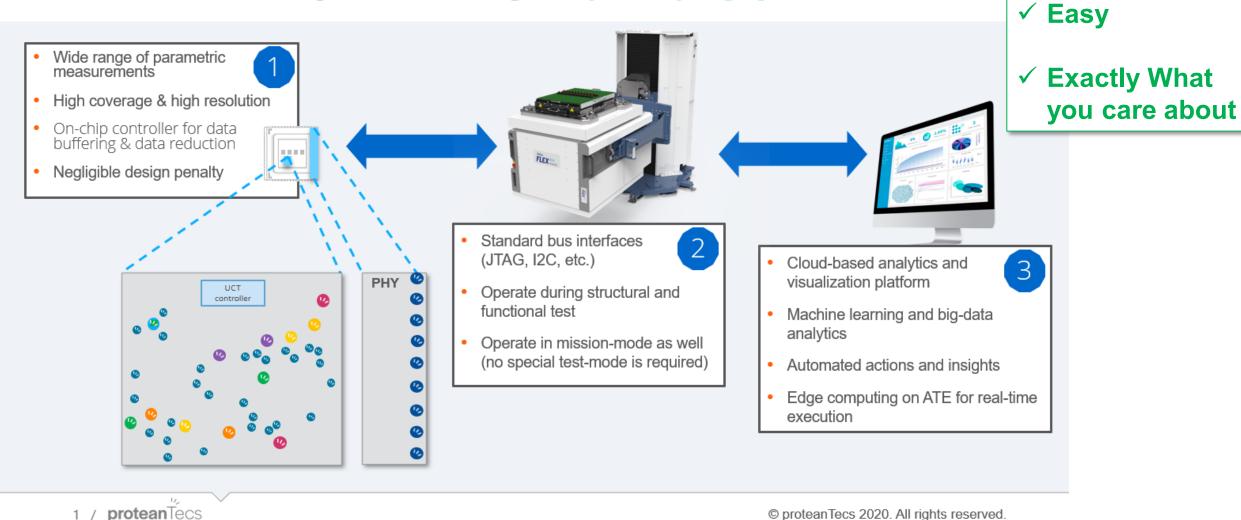

## Better Monitoring Technology Being Developed

# Universal Chip Telemetry™ (UCT) by proteanTecs

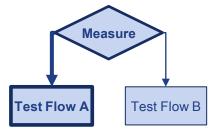

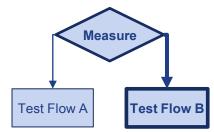

# Bringing It All together – What Can the Tester Do?

- Rapidly collect DUT response to

- Pattern Content, speed and sequencing

- Test Flow

- Power supply

- Export Data for offline analysis

- Test management between insertions

- Optimize scan network settings

- Host real-time machine learning

- Optimize test flow and conditions

- Use collected data to improve ATC response time

- Make sure ATC system is activated before DUT temperature rises

#### What Are the Technical Challenges?

- Device test flows can change on the fly for other reasons

- Device harvesting and down-grading

- Retests

- Trim and repair

- Will require more information from design

- more meta-data

- Multisite testing compounds the issue

- ATC must be site-aware

- All this combines to make predictive modeling more difficult

#### So, Back to Cost....

#### What may limit gains?

- Test flows get too dynamic and there are too many permutations to deal with

- Scan becomes a smaller portion of overall test time so throughput gains are limited

- All the extra work increases time to market, which can have a larger business impact than either test time or yield

- More data to deal with...

#### What are the opportunities?

- Faster test times

- Better yields because die temperatures are better controlled

- Optimization of test flows

- Methodology can be extended for other parameters like Vdd and reference voltages

#### Questions?

Special thanks to our colleagues .....

# Thank you sponsors!

## **ADVANTEST**®

A **global leader** in the ATE industry with a WW installed base of over 30,000 systems

Our nanotechnology products support leading-edge semiconductor processes at the **1Xnm node**

Our diverse workforce includes **5,500 employees** from **50 countries**

**Eco-friendly policies** emphasize reduction of our carbon footprint

2018 Global Technology Leader by Thomson Reuters

60+

Innovating in the measurement arena for **60+ years**

A VLSIresearch 10 BEST supplier for 32 consecutive years

# Amkor's Differentiators

#### Technology

Advanced Packaging Leadership

Engineering Services

Broad Portfolio

# Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

# Premier Assembly Materials Designer and Manufacturer:

- Thermal Interface Materials

- Liquid Metals

- Hybrid Metal TIMs

- Heat-Spring<sup>®</sup>

- Solder Pastes, Fluxes, Preforms, Alloys, Wire, and Bars

- Semiconductor Fluxes and Pastes

- Metals and Compounds

Free technical content at your fingertips

www.indium.com/insiderseries

# **COPYRIGHT NOTICE**

This presentation in this publication was presented at **Too Hot to Test** (February 9-11, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org