## **Shift Left**

Dave Armstrong

All Rights Reserved - ADVANTEST CORPORATION

### Goals

- 1. What are the trends?

- 2. What industry changes are driving this shift?

- 3. What are the financial implications of this shift?

- 4. How is this shift implemented?

- 5. Risk of over-testing.

- 6. Contributions of this approach.

#### What is the Trend?

Some people are shifting logic level test content to the right - into system level test.

→ Is this the best thing to do?

**Lower Cost Solution = Shift Left**

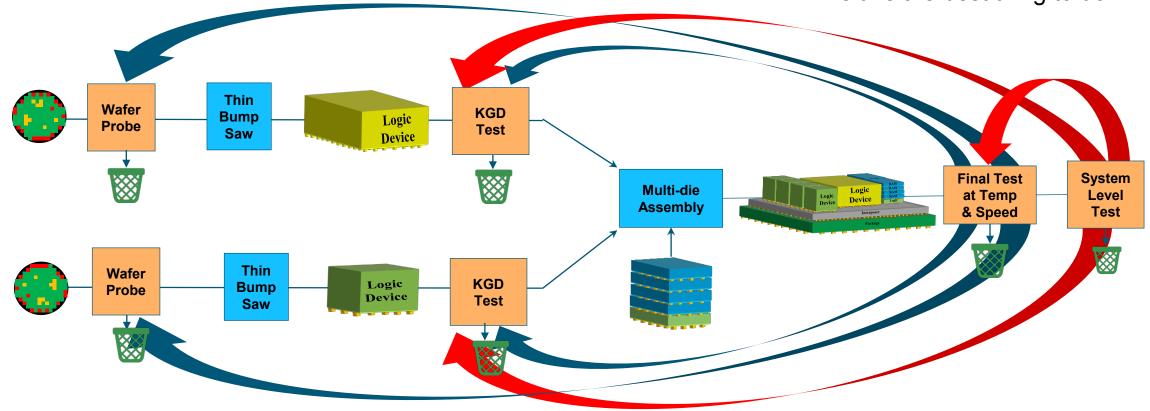

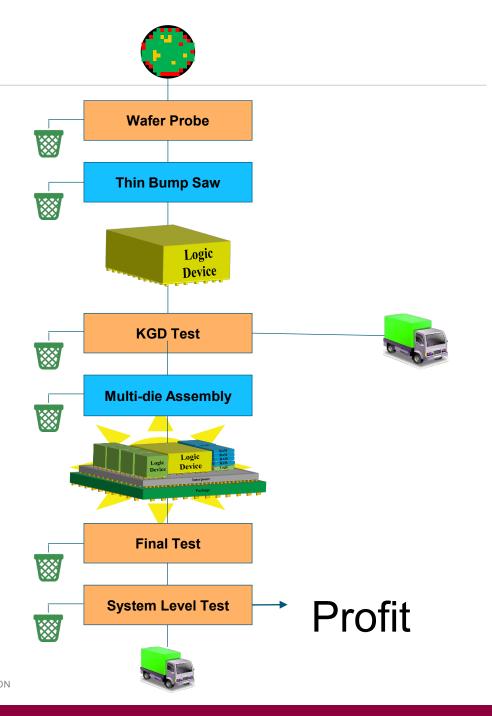

# **Description of Typical Un-Shifted Test Steps**

| Test Step                | Typical Goals                                                                                                                                                                                          | Test Cell                                                     |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|

| Wafer Test Step          | <ul><li>Find hard rejects.</li><li>Confirm scan &amp; functionality at one temp.</li></ul>                                                                                                             | Automatic Test Equipment (ATE) +<br>Wafer Prober              |  |

| KGD Test Step            | <ul> <li>Confirm scan &amp; functionality at a second temp</li> <li>Find assembly defects</li> </ul>                                                                                                   | ATE + Reconstituted die prober or ATE + Singulated die prober |  |

| Final Test Step          | <ul> <li>Packaged device test</li> <li>Extended scan tests</li> <li>Parametric performance test</li> <li>At-speed tests</li> <li>High-power tests</li> <li>Stress tests</li> <li>Shift Left</li> </ul> | ATE + Active Thermal Control (ATC) ATC + Device/Die Handler   |  |

| System Level Test Step ( | <ul><li>Packaged device test</li><li>Boot up tests</li><li>Fuse blowing</li></ul>                                                                                                                      | System Level Tester (SLT) + ATC + Device handler              |  |

# Why is "Shift-Left" Happening?

1. More test sooner → more profitable products.

More heterogeneous integration → Parts need to be of a higher quality level (KGD)

3. Shippable unit is changing → Final Test or SLT need to be done on raw die.

### **Unfortunate KGD Realities...**

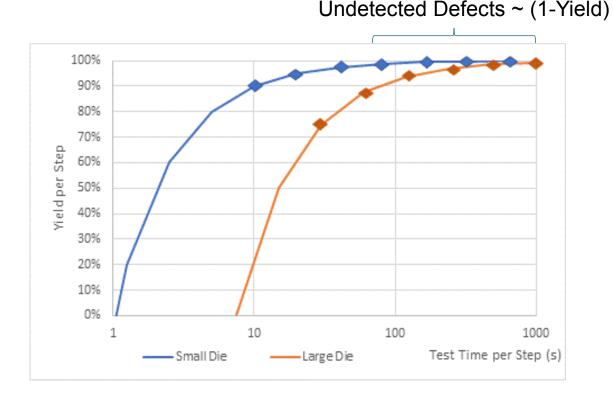

Question: If I get a 90% yield at wafer probe – what percentage of the possible faults did I cover?

Answers: Yield only states what percentage of the parts tested were bad.

The passing parts may or may not be 100% good.

Question: If I spend 10s of test time to get a 90% yield with a high fault coverage, how much

time and fallout must I spend to find all the failing devices?

Answers: The law of diminishing returns suggests more time is needed for more coverage.

Exponential coverage curve asymptotically approaches 100% but never gets there.

# "Reasonable" Assumptions

1. For the sake of this presentation let's assume that half the remaining faults are detected in the next step which is twice as long.

| Test<br>Step | Yield        | Test<br>Time |  |

|--------------|--------------|--------------|--|

| 1            | 90%/75%      | 10s/30s      |  |

| 2            | 95%/87.5%    | 20s/60s      |  |

| 3            | 97.5%/93.75% | 40s/120s     |  |

| 4            | 98.75%/96.9% | 80s/240s     |  |

The faults found per test step is proportional to the area over the curve.

2. This presentation scales the cost estimates based on the raw cost of a small 10x10 mm die cost. All cost estimates are shown relative to this cost in recognizing that cost ratios tend to be more consistent while absolute costs may vary from technology to technology and/or company to company.

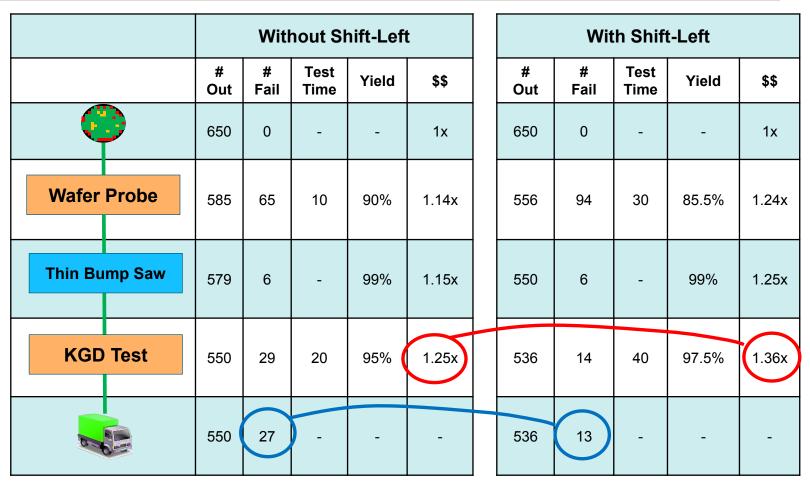

### How Much Cost Savings – Small Device Shipping as KGD

#### **Assumptions**

|                             | Small Device                        |

|-----------------------------|-------------------------------------|

| Technology                  | 10 nm                               |

| Die per wafer               | 650                                 |

| Wafer Probe Test Time       | 10                                  |

| Sites                       | 4                                   |

| Wafer Probe Yield           | 90%                                 |

| Next step Test-time & Yield | Per Assumption on<br>Previous slide |

#### Note:

Values given for example only. Your results will vary.

Shifting left reduced unfound failures shipped by 51% Shift left cost 9% more to manufacture

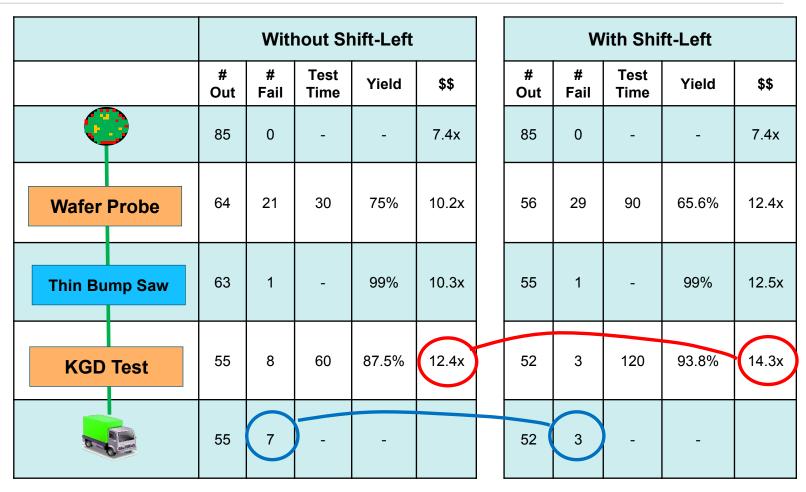

### How Much Cost Savings – Large Device Shipping as KGD

#### **Assumptions**

|                             | Large Device                     |

|-----------------------------|----------------------------------|

| Technology                  | 10 nm                            |

| Die per wafer               | 85                               |

| Wafer Probe Test Time       | 30                               |

| Sites                       | 1                                |

| Wafer Probe Yield           | 75%                              |

| Next step Test-time & Yield | Per Assumption on<br>Prior slide |

Note: Values given for example only. Your results will vary.

Shifting left reduced unfound failures shipped by 53% Shift left cost 16% more to manufacture

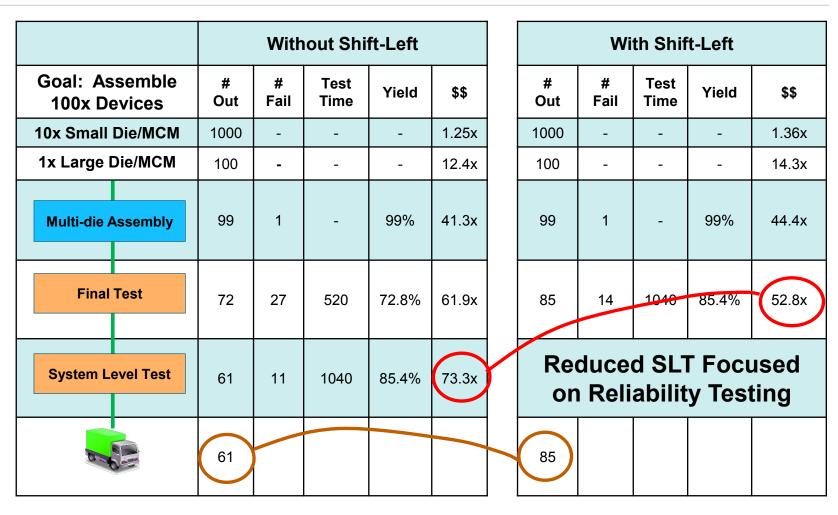

### **How Much Cost Savings – Multi-Chip Module**

#### **Assumption:**

- Zero cost attributed to packaging & assembly (Shift-left did save the cost of 13x interposers & substrates.)

- Test costs attributed based on test-time and typical hourly costs for ATE, prober, and SLT.

#### Note:

Values given for example only. Your results will vary.

Shift left cost 28% LESS cost to manufacture Shipped 37% more parts shipped.

# What System Changes are Needed to Do This?

| Shift-Left Change              | Key Capabilities                                          | Necessary Changes                                                                                                                                                                                                                                   |

|--------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Final-Test → KGD Test          | At-speed tests<br>High-Power ATC                          | ATE: High-speed instruments ATE: Higher power supplies ATC: T-Junction feedback per DUT Probes: Higher Current Carrying Capacity (CCC) probes Probes: Higher-frequency probes Prober: Singulated Die Handler or Frame Handler if temp not too high. |

| KGD Test → Wafer Test          | Two temp testing. Crack detection.                        | ATE: Extended test sequence ATC: High & Low temp testing                                                                                                                                                                                            |

| System Level Test → Final-Test | High-Power ATC<br>High-speed interfaces<br>Device boot-up | ATE: System focused environment. Software: System focused code.                                                                                                                                                                                     |

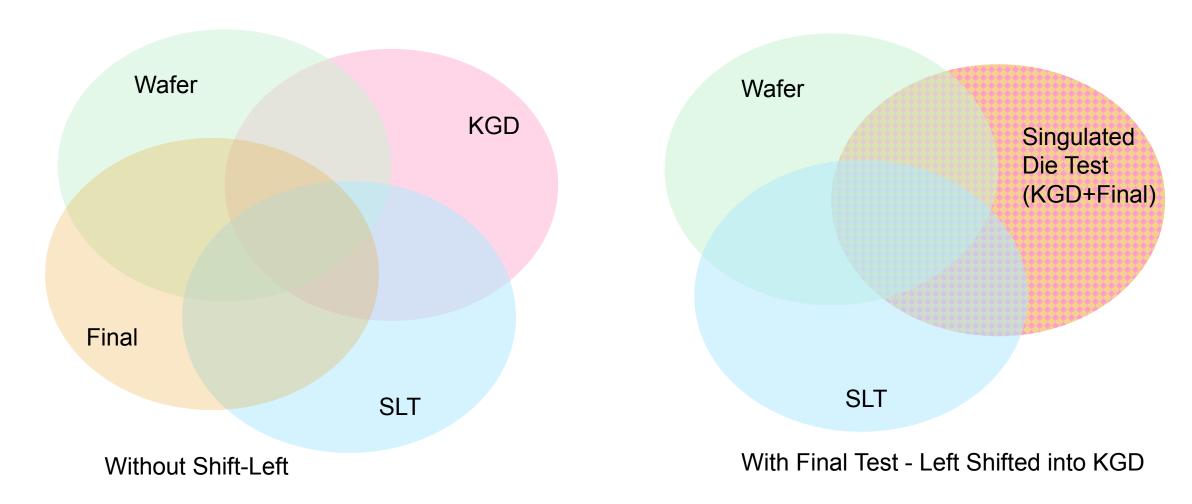

# What About Over-Testing?

Fewer Test Steps

Less Over-Testing (and less handling)

### This Presentation Has ...

- Shown how test content is a valuable resource which is best deployed where it can provide the maximum value.

- b. Confirmed what may be obvious, that by doing more tests sooner you can ship significantly higher quality die-level products for a small increase in product cost.

- c. Calculated that "KGD" product quality can improve significantly for a small incremental cost by shifting test content to the left.

- d. Shown that by shifting test-content to the left, one can ship more multi-chip modules sooner, with a lower cost.

- e. Pointed out some of the test-sequence changes and equipment enhancements which need to be considered when exploring this concept.

# Backup

# **Assumptions**

Wafer Test Step

KGD Test Step

Final Test Step

System Level Test

| Parameter   | Value |

|-------------|-------|

| \$/Hour     | \$140 |

| Wafer Load  | 225s  |

| Utilization | 85%   |

| Index time  | 0.75S |

| Parameter   | Value |  |

|-------------|-------|--|

| \$/Hour     | \$140 |  |

| Wafer Load  | 225s  |  |

| Utilization | 85%   |  |

| Index time  | 0.75S |  |

| Parameter   | Value |

|-------------|-------|

| \$/Hour     | \$145 |

| Sites       | 1     |

| Utilization | 85%   |

| Index time  | 1.5s  |

| Parameter   | Value |

|-------------|-------|

| \$/Hour     | \$50  |

| Sites       | 8     |

| Utilization | 85%   |

| Index time  | 4s    |

#### **Un-shifted Assumptions**

| Small Test Time / Sites | 10s / 4 | 20s / 1 | 40s / 1  | 80s / 1               |

|-------------------------|---------|---------|----------|-----------------------|

| Large Test Time / Site  | 30s / 1 | 60s / 1 | 120s / 1 | 240s / 1              |

| MCM Test Time / Site    | N/A     | N/A     | N/A      | 1040s (10*80+240) / 8 |

# Thank you sponsors!

# **ASE - Expanding Our Role in the Electronics Ecosystem**

The Industry's most comprehensive toolbox Providing a complete value chain solution

### **ADVANTEST**®

A **global leader** in the ATE industry with a WW installed base of over 30,000 systems

Our nanotechnology products support leading-edge semiconductor processes at the **1Xnm node**

Our diverse workforce includes **5,500 employees** from **50 countries**

**Eco-friendly policies** emphasize reduction of our carbon footprint

2018 Global Technology Leader by Thomson Reuters

60+

Innovating in the measurement arena for **60+ years**

A VLSIresearch 10 BEST supplier for 32 consecutive years

## **Carrier Solutions for Known Good**

#### **Vacuum Release Carriers**

Pocketless Trays for Automated KGD Handling

#### **Gel-Box • Gel-Tray • Gel-Slide Carriers**

Carriers for Manual KGD Handling

#### **NEW** Carrier Films

- Reconstituted Known Good Wafer Handling

- **Universal Carrier**

- Custom Constructions

- Low Tack, Low Residue

- Textured Available

www.gelpak.com 1-888-621-4147

### Mühlbauer Group

MUHLBAUER, INC. 226 Pickett's Line Newport News, VA 23603-1366 U.S.A.

Tel.: +757-947-2820 Fax: +757-947-2930

E-mail: info@muhlbauer.com Web: www.muhlbauer.com

# COPYRIGHT NOTICE

This presentation in this publication was presented at the Known Good Die (KGD) Workshop 2020. The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC, IMAPS, or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.kgdworkshop.org www.meptec.org