# Road to Chiplets: Design Integration

May 10-12, 2022

# 3D-IC (3DHI) Design Challenges

John Park (jpark@cadence.com)

Product Management Group Director

cādence

# Introduction

**Ecosystem Challenges**

Packaging Challenges

SoC/ASIC (3D Integration) Challenges

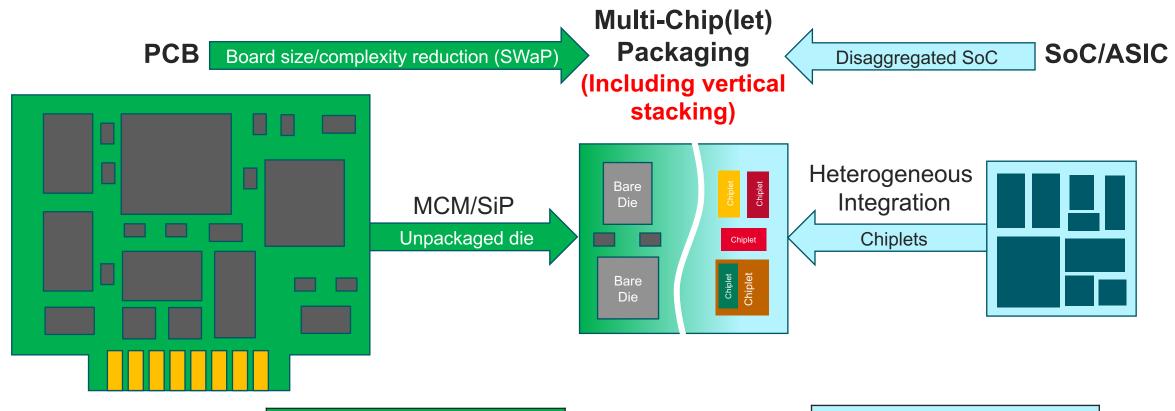

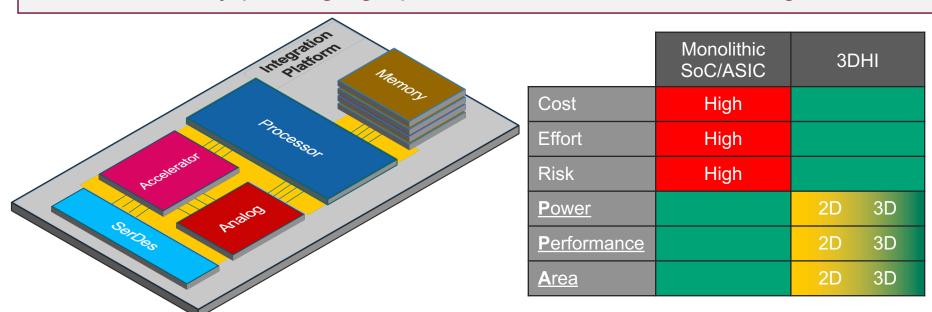

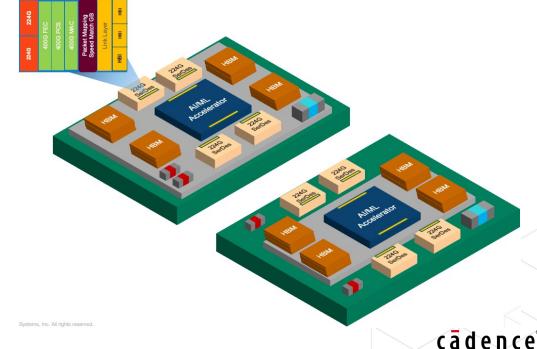

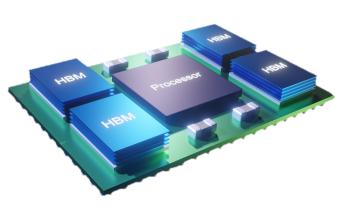

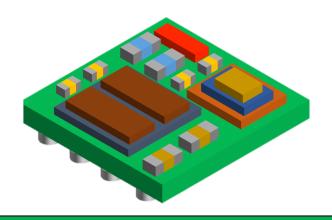

### SiP/MCM vs. Chiplet-Based 3DHI Architectures

| PCB to MCM/SiP Benefits |

|-------------------------|

| Smaller footprint       |

| PCB simplification      |

| Higher bandwidth        |

| Lower power             |

#### **SoC to HI Benefits** Reduced NRE costs Shorter time to market Larger than reticle size designs More flexible IP use-model

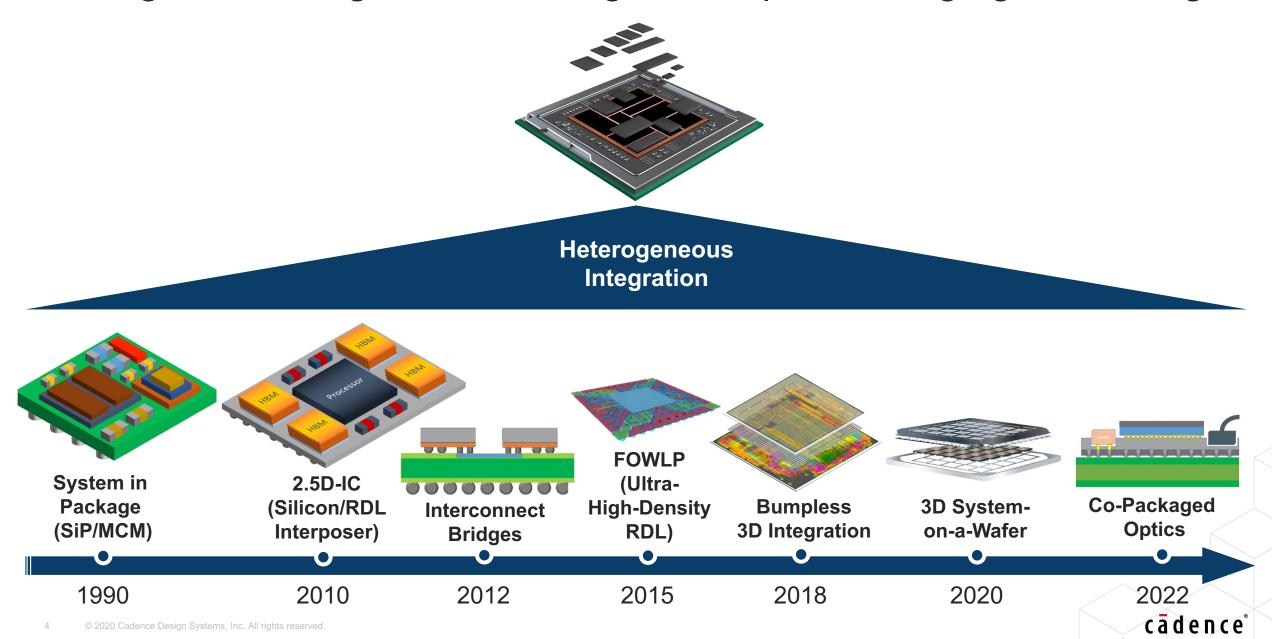

# Heterogenous Integration Leverages Multiple Packaging Technologies

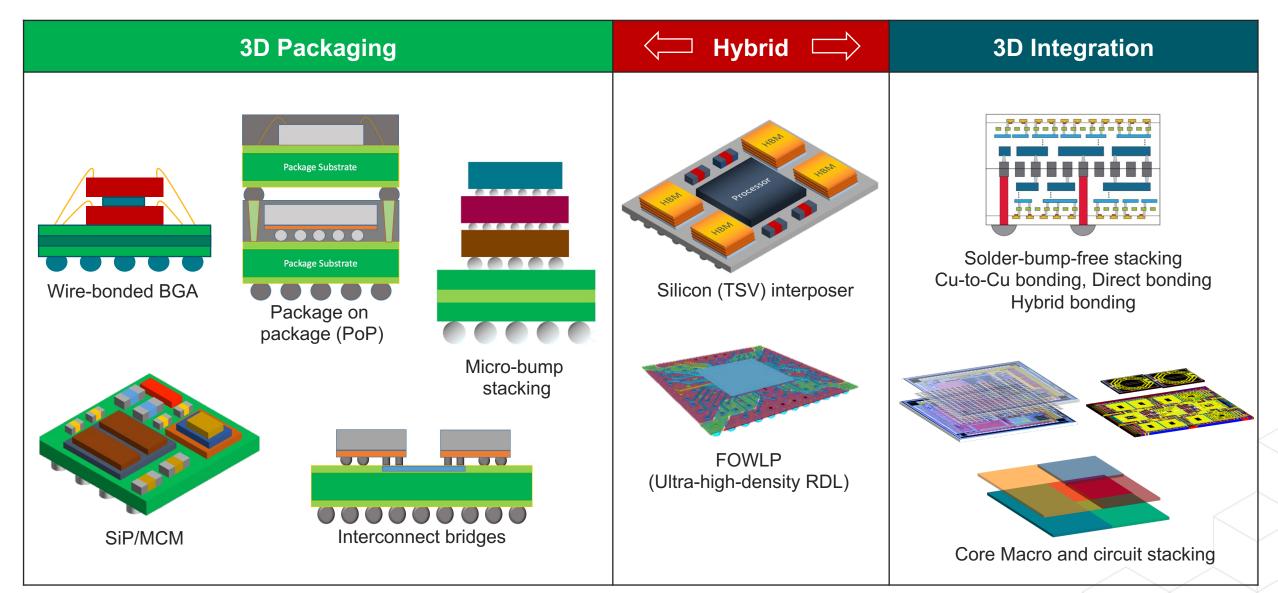

# 3D Packaging (Back-End 3D) vs. 3D Integration (Front-End 3D)

# 3DHI Ecosystem Challenges

### **Assembly Design Kits (ADK)**

- PDK equivalent for the entire multi-chiplet assembly

- Historically, OSATs have not provided sufficient data to package designers

- OSATs have large design centers to off-set this limited formal sharing of design requirements

- Foundries are helping to drive the concept of a PDK into the packaging world

#### Layer stack-up

Material

**Properties**

Thickness

Physical/Electrical layout constraints

Line and space

Differential signaling

Customized in-design **DRCs**

#### **Design Libraries**

#### **Footprints**

Discrete

BGA/LGA

Via structures

3D Mechanical

Bond-Wire profiles

Parametrized RF structures

Thermal models

Power models

#### **Assembly Rules**

Device placement constraints based on assembly pick & place equipment

Die to die spacing

Device to device

Device to obstacle

Jitter tolerance

Insertion loss

Eye mask

#### Compliance Kits

Electrical spec validation of chip(let)-to-chip(let) interfaces

Interconnect library

IO libraries

Eve masks

Return loss

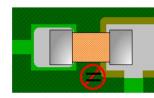

#### Manufacturing Rules

#### Board/substrate manufacturing process

Substrate checks

Soldermask checks Soldering issues

Silkscreen checks

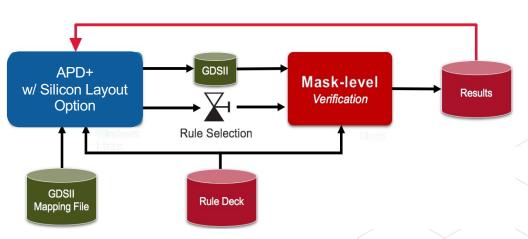

# Rule Decks

Foundry/ semiconductor manufacturing process

> DRC LVS

Metal fill

Die/Chiplet Overhang

Die/Chiplet Center to Center Offset

Die/Chiplet Spacing to Substrate Edge

Die/Chiplet to Die/Chiplet Spacing

Tombstone Effect (% size diff)

# 3DHI Ecosystem Challenges

#### Commercialization and Standards for Chiplets

- Most chiplet-based designs are in a closed ecosystem

- Business case for IP companies to provide 3<sup>rd</sup> type of IP

- Standard exchange formats are lacking

- Common communication interface

- o AIB, UCIe, BoW, OpenHBI, ...

- Too many packaging options to standardize on a single interface

| Interface Considerations<br>Serial, Parallel or Proprietary |

|-------------------------------------------------------------|

| Package type                                                |

| Reach (on/off package)                                      |

| Power (pJ/bit)                                              |

| Latency                                                     |

| Speed                                                       |

| Bandwidth                                                   |

| Routing complexity                                          |

| Test, ESD, ???                                              |

# 3DHI Ecosystem Challenges

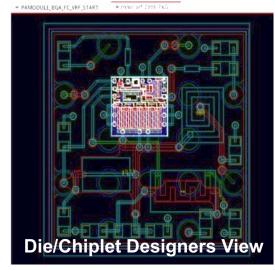

#### Complex Design Methodologies

- Explosion in the number of design tools required

- Design tools than support multiple PDKs (Tech LEF) in a single layout canvas

- Collaboration/co-design across multiple tools, design teams (Digital, RF, Systems) and across multiple companies

- Design partition strategies including D2D chiplets, thermal and off-package IO

- Limited capabilities for rapid prototyping with risk mitigation strategies

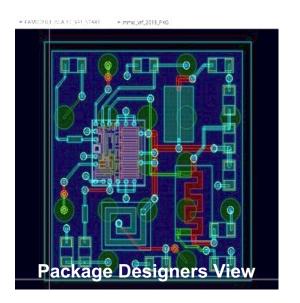

# 3DHI Challenges for the Package Designer

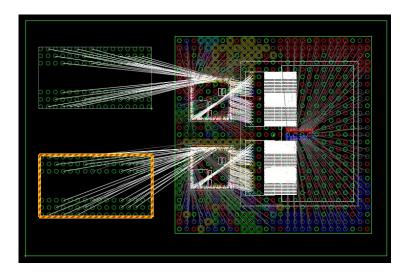

#### **Cross-Domain Co-Design**

- Concurrent planning/editing/optimization environment for IC, package and PCB

- Abstract-level for early planning

- Detailed-level for physical co-design

- Tight-loop ECO process between chiplet, package and PCB designs

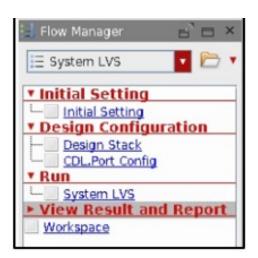

- System-level LVS with support for rule-deck-free methodology

- Intelligent front-end (schematic/table) connectivity-capture-based flow

# 3DHI Challenges for the Package Designer

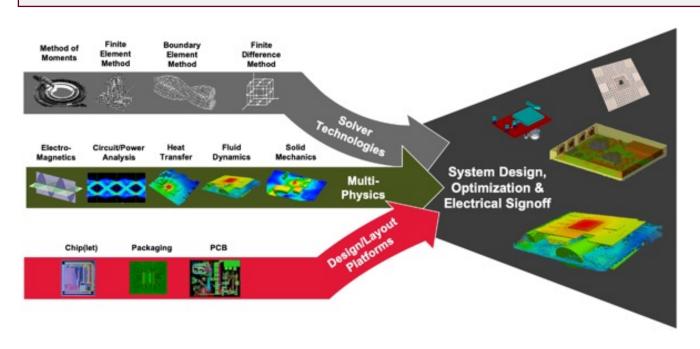

### System-Level Analysis (SI)

- PCB-like analysis capabilities

- Pre- and post-route chiplet-to-chiplet signal integrity and compliance

- System-level power analysis

- Multi-physics analysis

- On-die EM/IR coupled with off-die electromagnetics

# 3DHI Challenges for the Package Designer

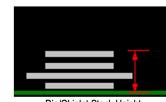

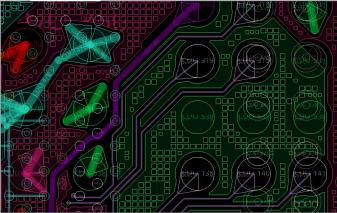

#### Silicon-Based Packaging Technologies

- Transitioning from laminate design to silicon design

- Formal sign-off of DRC and LVS

- Differing power/ground routing styles

- Stripes/rails and/or copper pour

- Advanced metal balancing

- Design capacity

- Tens of thousands to hundreds of thousands (or more)

# 3DHI Challenges for the ASIC/SoC Designer

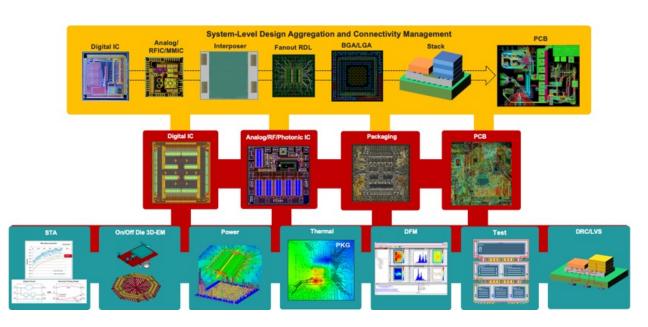

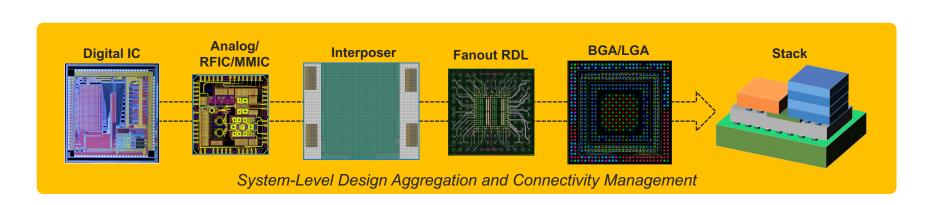

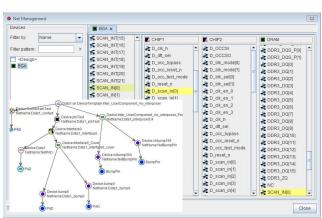

### **System-Level Design Aggregation**

- Concurrent planning/editing/optimization environment for IC, package and PCB

- Common database for entire 3D-IC system

- Chips, chiplets, tiles, packaging and PCB

- Early-stage thermal/power analysis

- Hierarchical netlisting

- Source of golden/sign-off netlist

- Partitioning by integration level

# 3DHI Challenges for the ASIC/SoC Designer

#### **True Multi-Chiplet 3D Implementation**

- Design size capacity

- Concurrent editing of multiple devices at full transistor-level detail

- No abstraction

- Homogenous and heterogenous

- On-the-fly die splitting and re-partitioning in Z direction

- Timing driven cross-chip(let) routing

- Support for 3D-IC test standards

# 3DHI Challenges for the ASIC/SoC Designer

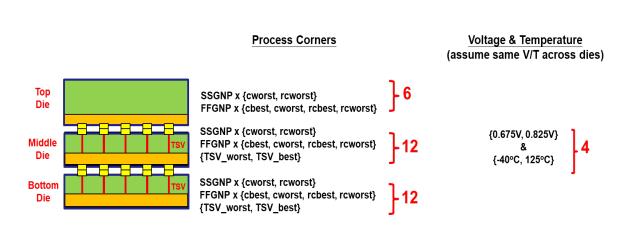

#### 3D-Enabled Analysis and Sign-Off

- STA with automated corner reduction

- Rule-deck-free system-level LVS

- Alignment and connectivity checking

- Multi-die EMIR

- Accounting for dynamic loading across multiple die

- Comprehensive thermal stress and CMP planarity checks

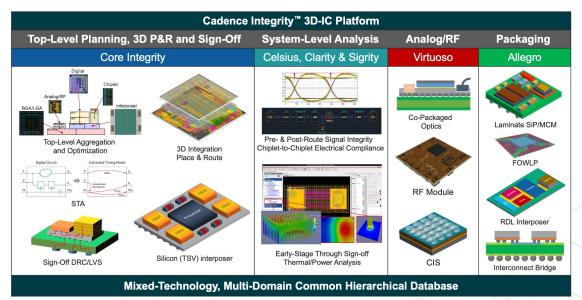

# What to Look for in a Next-Generation 3D Integration Platform...

#### **High-Capacity Common 3D-IC Platform** Top-Level Planning, 3D P&R and Sign-Off **System-Level Analysis** Analog/RF **Packaging** Analog/RF Interposer BGA/LGA Signal Integrity **BGA/SiP/MCM** Co-Packaged **Optics** 3D Integration System-Level Aggregation Place & Route and Optimization **FOWLP** STA **RF Module** Early-Stage Thermal/Power Analysis

Mixed Technology, Multi-Domain Common Database

Sign-Off DRC/LVS

Silicon (TSV) Interposer

# Summary

Advanced Packaging and 3DHI are Driving More-Than-Moore

Heterogenous Integration Leverages Multiple Packaging Technologies

Several New Challenges Facing Designers Moving to 3DHI

Is it Time to Reevaluate Your Design Methodology?

© 2020 Cadence Design Systems, Inc. All rights reserved worldwide. Cadence, the Cadence logo, and the other Cadence marks found at <a href="www.cadence.com/go/trademarks">www.cadence.com/go/trademarks</a> are trademarks or registered trademarks or registered trademarks or registered trademarks or Accellera and Systems Initiative Inc. All Arm products are registered trademarks or trademarks or trademarks or service marks owned by MIPI Alliance. All PCI-SIG specifications are registered trademarks or trademarks are the property of their respective owners.

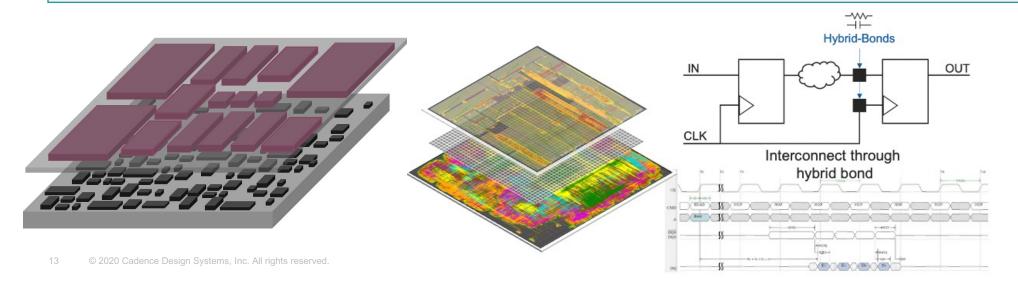

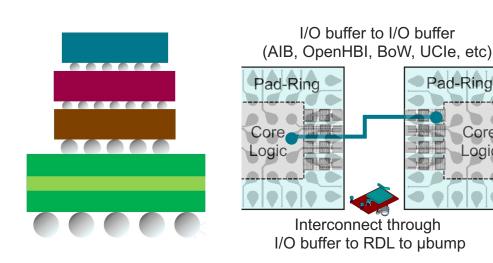

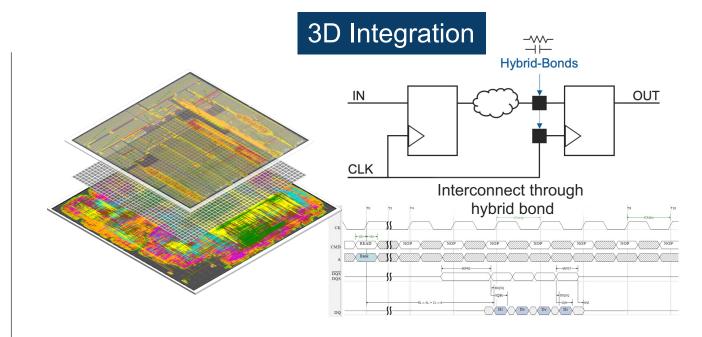

### 3D Packaging Versus 3D Integration

### 3D Packaging

- (Micro)Bumped

- Timing closed/signoff each die separately

- Typically, no concurrent design of the dies

- Common approach for Memory and CIS for over 5 years

- Bump-less (Hybrid-bond/Cu-to-Cu bond, Direct bond)

- No I/O buffers between die/macros

- Concurrent design/analysis mandatory

- Timing-driven routing and STA required for digital designs

- Cross-die/chiplet route resource sharing

- Z-dimension placement

# Why Can't We Have One Tool Than Can Design Everything?

|                       | Package/PCB                                                                                                                                  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Use-Model             | GUI-centric interactive place & route                                                                                                        |

| Placement             | Tens of devices, mechanical structures/restrictions, 3D assembly rules Abstract representation of die(s)/chiplet(s)                          |

| Routing               | Constraint-driven, push/shove 45-degree/all-angle routing, vias larger than traces, metal fill power planes. Passive interconnect substrates |

| Capacity/Performance  | 100,000s                                                                                                                                     |

| Extraction/Analysis   | 3D-EM, System-Level SI/PI, IO-to-IO timing                                                                                                   |

| Manufacturing Outputs | Board/Substrate (informal sign-off)                                                                                                          |

| OS                    | Windows                                                                                                                                      |

| IC                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------------------------------|

| Batch/script driven fully automated design                                                                                         |

| Hundreds-of-thousands of instances, standard-<br>cells (all the same height) and macros,<br>partitioned into multiple blocks       |

| Timing-driven routing, 90-degree, Vias smaller than metal routing, gridded power routing. Active (device + metal layers) substrate |

| 1,000,000,000s                                                                                                                     |

| RC extraction, Flop-to-flop timing                                                                                                 |

| Foundry (formal sign-off DRC/LVS)                                                                                                  |

| Linux                                                                                                                              |

### **COPYRIGHT NOTICE**

This multimedia file is copyright © 2022 by MEPTEC. All rights reserved. It may not be duplicated or distributed in any form without prior written approval.

The content of this presentation is the work and opinion of the author(s) and is reproduced here as presented at the **Road to Chiplets: Design Integration** (May 10-12, 2022).

The MEPTEC logo and 'MEPTEC' are trademarks of MEPTEC.

www.meptec.org