# Road to Chiplets: Design Integration

May 10-12, 2022

www.meptec.org

# SUBSTRATE DESIGN OPTIMIZATION FOR CHIPLET ARCHITECTURE

#### DEEPAK KULKARNI

AMD FELLOW

ADVANCED PACKAGING

#### CAUTIONARY STATEMENT

This presentation contains forward-looking statements concerning Advanced Micro Devices, Inc. (AMD) such as the features, functionality, performance, availability, timing and expected benefits of AMD products and technology as well as technology trends, innovation and roadmaps, which are made pursuant to the Safe Harbor provisions of the Private Securities Litigation Reform Act of 1995. Forward-looking statements are commonly identified by words such as "would," "may," "expects," "believes," "plans," "intends," "projects" and other terms with similar meaning. Investors are cautioned that the forward-looking statements in this presentation are based on current beliefs, assumptions and expectations, speak only as of the date of this presentation and involve risks and uncertainties that could cause actual results to differ materially from current expectations. Such statements are subject to certain known and unknown risks and uncertainties, many of which are difficult to predict and generally beyond AMD's control, that could cause actual results and other future events to differ materially from those expressed in, or implied or projected by, the forward-looking information and statements. Investors are urged to review in detail the risks and uncertainties in AMD's Securities and Exchange Commission filings, including but not limited to AMD's most recent reports on Forms 10-K and 10-Q.

AMD does not assume, and hereby disclaims, any obligation to update forward-looking statements made in this presentation, except as may be required by law.

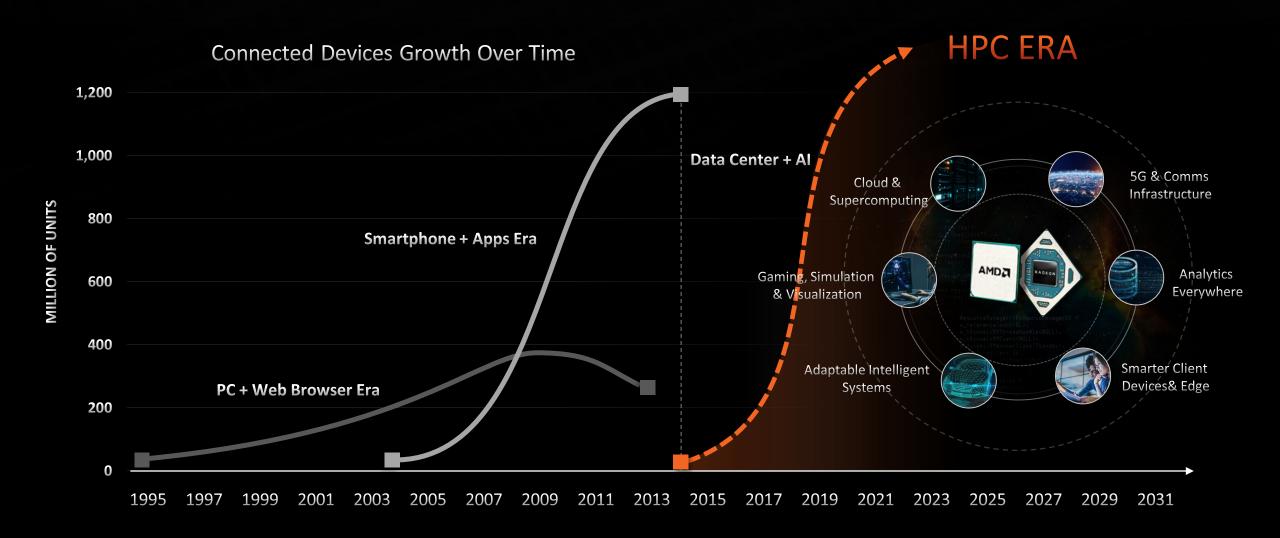

#### EXPLOSION OF CONNECTED DEVICES

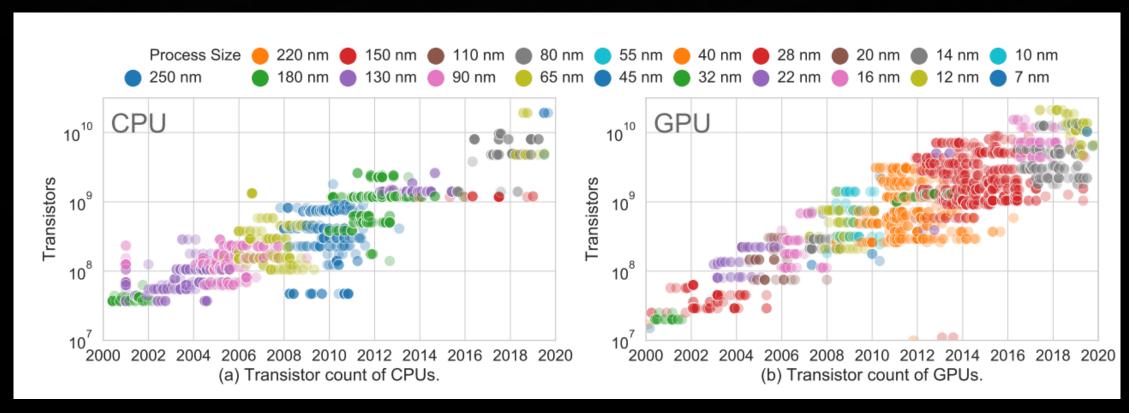

#### **GROWING COMPLEXITY OF CPU & GPU**

Courtesy: Yifan Sun, et.al., 2019, Summarizing CPU & GPU design trends with Product data, ArXiv

CPU & GPU transistor counts continue to grow at exponential rates In many cases high-end devices exceeding silicon reticle limits

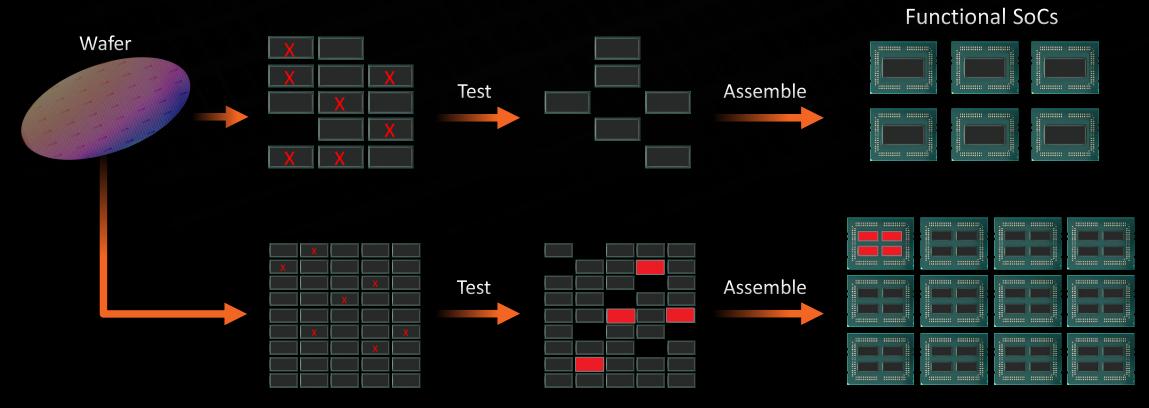

## HIGH-LEVEL APPROACH TO CHIPLETS

**Many More Functional SoCs** Ability to mix and match at a finer grained level

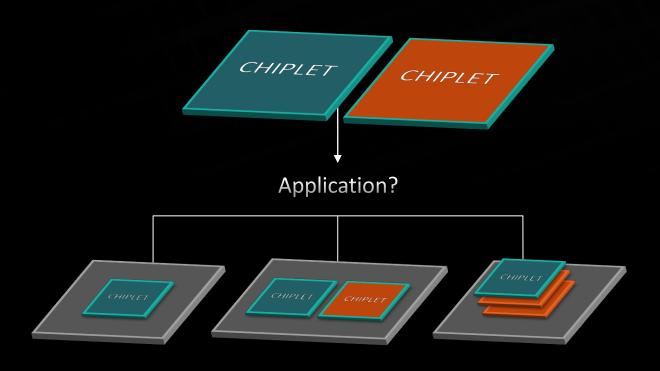

## MODULAR ARCHITECTURE GOALS

#### **ENABLING A MORE FLEXIBLE APPROACH**

- We want to build tailored products for specific markets by mixing and matching chiplet types

- We can now specialize a domain specific chiplet and include more or fewer of them for a given product

- More domain-specific products at higher yields ... provided we can build low-overhead chiplets

#### ROLE OF SUBSTRATES

#### INCREASED INTEGRATION ON PACKAGE

3RD GEN AMD EPYC™ CPU WITH AMD 3D V-CACHE

- More complex substrates with higher body size, layer count

- Increased power delivery demand

- Increased data rates driving novel HSIO solutions

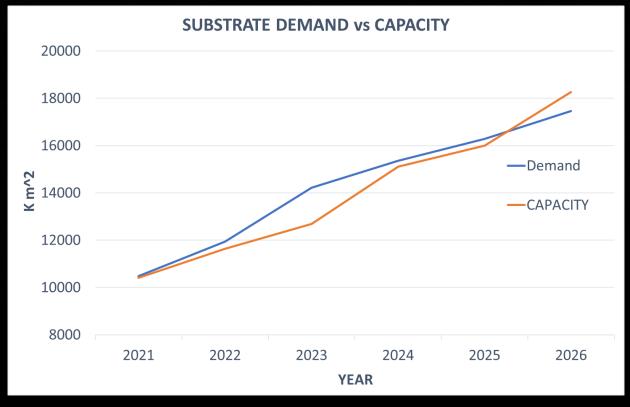

# SUBSTRATE CAPACITY CHALLENGES

Courtesy: TechSearch

CPU, GPU packages continue to grow in complexity

Demand for substrates continues to outstrip supply till 2026

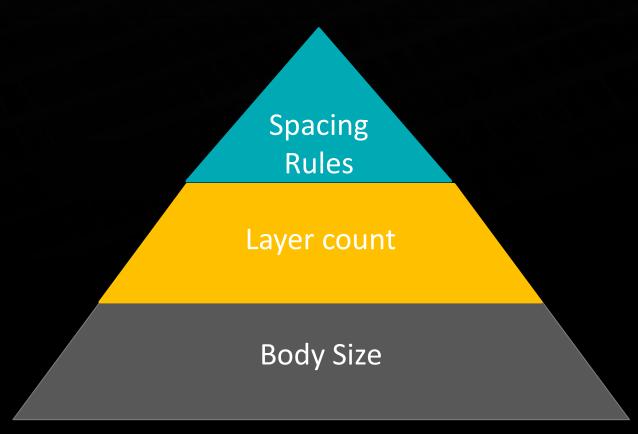

#### SUBSTRATE DESIGN OPTIMIZATION

Co-optimization with silicon floor plan

PD/SI routing requirements

Top & Bottom side fit study

Board requirements

Maximize spacing

DFY

Optimize layer count and routing density DFM

Minimize body size to improve panel utilization

Design for Manufacturing & Design for Yield need to be initiated from concept phase to enable co-optimization of product design

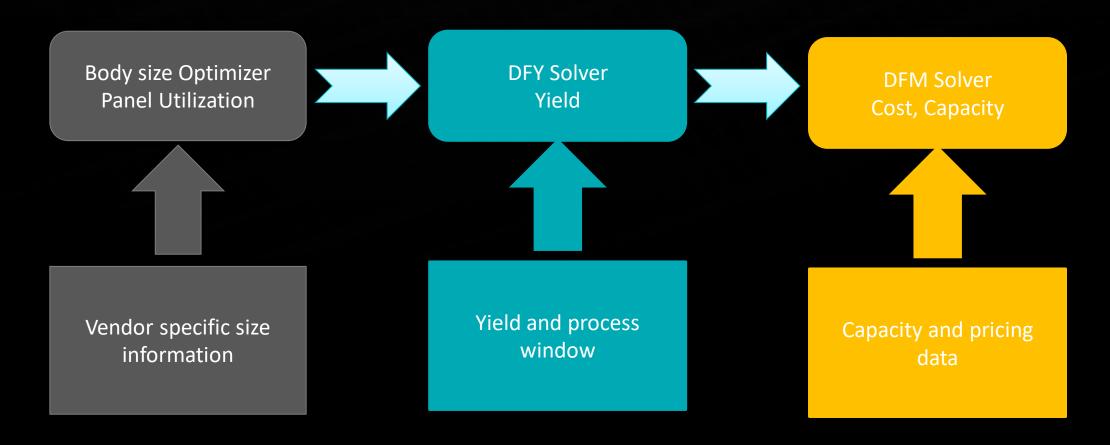

#### **END-TO-END ANALYTICS**

End-to-end analytics tools developed to 'learn' from historical data and provide quantifiable metrics for co-optimization

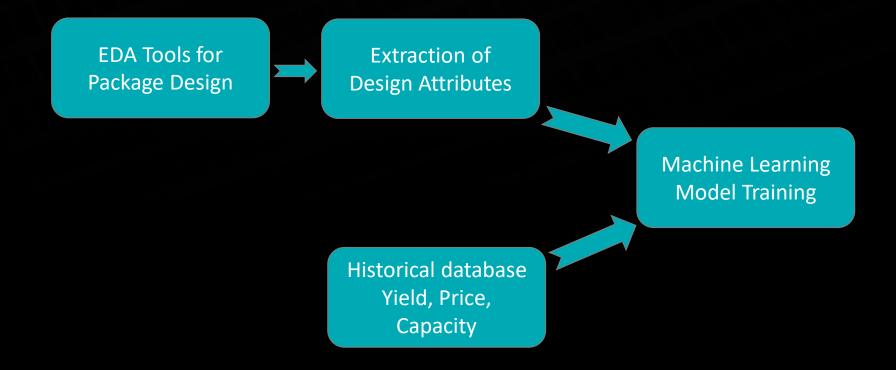

# DFM/DFY: MACHINE LEARNING APPROACH

#### TRAINING METHODOLOGY

Model trained based on historical database of design, yield, cost, and capacity

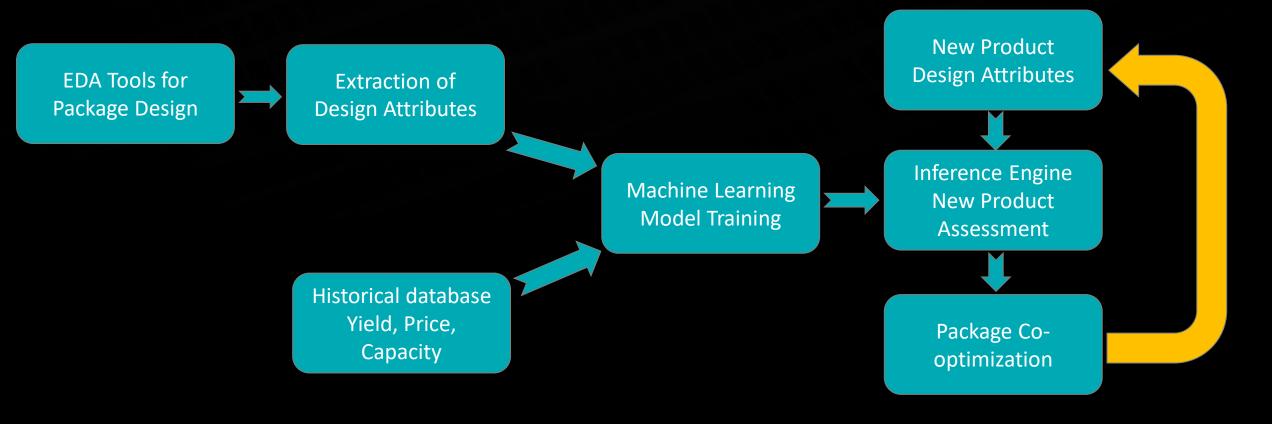

# DFM/DFY: MACHINE LEARNING APPROACH

#### CONTINUOUS LEARNING & OPTIMIZATION

Methodology provides framework for continuous learning and optimization

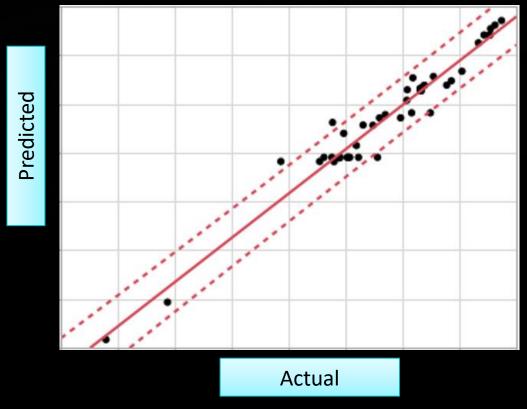

# DFY/DFY: MACHINE LEARNING RESULTS

Machine learning model shows good correlations to actual data

# BENEFITS OF DFM/DFY OPTIMIZATION

10% to 30% CAPACITY IMPROVEMENT

Significant improvement in capacity through design optimization

#### ROAD AHEAD

- 2.5D & 3D packaging continues to blur the boundaries between silicon and package

- Design co-optimization needed to balance performance, cost and capacity

- Increasing design complexity expected to drive adoption of machine learning tools

- Opportunity for designers, EDA tool vendors, manufacturing firms to collaborate

#### COPYRIGHT AND DISCLAIMER

©2022 Advanced Micro Devices, Inc. All rights reserved.

AMD, the AMD Arrow logo, EPYC, Ryzen, Infinity fabric, and combinations thereof are trademarks of Advanced Micro Devices, Inc. Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

The information presented in this document is for informational purposes only and may contain technical inaccuracies, omissions, and typographical errors. The information contained herein is subject to change and may be rendered inaccurate for many reasons, including but not limited to product and roadmap changes, component and motherboard version changes, new model and/or product releases, product differences between differing manufacturers, software changes, BIOS flashes, firmware upgrades, or the like. Any computer system has risks of security vulnerabilities that cannot be completely prevented or mitigated. AMD assumes no obligation to update or otherwise correct or revise this information. However, AMD reserves the right to revise this information and to make changes from time to time to the content hereof without obligation of AMD to notify any person of such revisions or changes.

This information is provided 'as is." AMD makes no representations or warranties with respect to the contents hereof and assumes no responsibility for any inaccuracies, errors, or omissions that may appear in this information. AMD specifically disclaims any implied warranties of non-infringement, merchantability, or fitness for any particular purpose. In no event will AMD be liable to any person for any reliance, direct, indirect, special, or other consequential damages arising from the use of any information contained herein, even if AMD is expressly advised of the possibility of such damages.

#

#### **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Design Integration** (March 10-12, 2022). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org