# Road to Chiplets: Data & Test

November 9 - 11, 2021

Wu Yang

Technical & Foundry Programs Manager

Siemens EDA

**SIEMENS**

#### **Contents**

- Understanding 3DIC Market and Test Challenges

- IEEE1838 for 3DIC Testing

- 2.5 D Test Methodology

- 3D Stack Test Methodology

- Conclusion

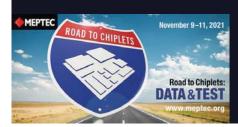

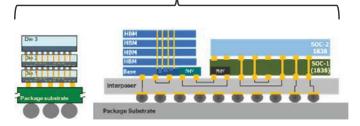

#### **Understand 2.5D and 3D Test Challenges**

3D (anticipate production 2022)

• More die DFT pins accessible at package

• DFT pins accessible only through base die

- Across die 1149.1 compatible TAP

- Scan data path

- Die pattern retarget to package

- Die2die tests

- Setup has to go through base die

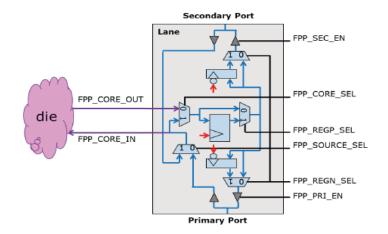

- Serial & flexible parallel port (FPP) support

- Cost, pin count, low power & automation

- Compliances to standards

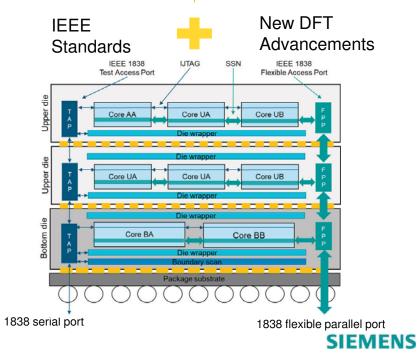

#### **IEEE1838 for 3DIC Testing**

#### IEEE 1838 addresses

- A standardized die DFT infrastructure for inter die integration

- Hardware and protocol

Possible logic between DWRs (die wrapper register) and IOs

#### IEEE1838 doesn't

- Differentiate requirements for 2.5D and 3D

- Provide an operation language

- Discuss how to do the DFT and test

Flexible parallel port (FPP)

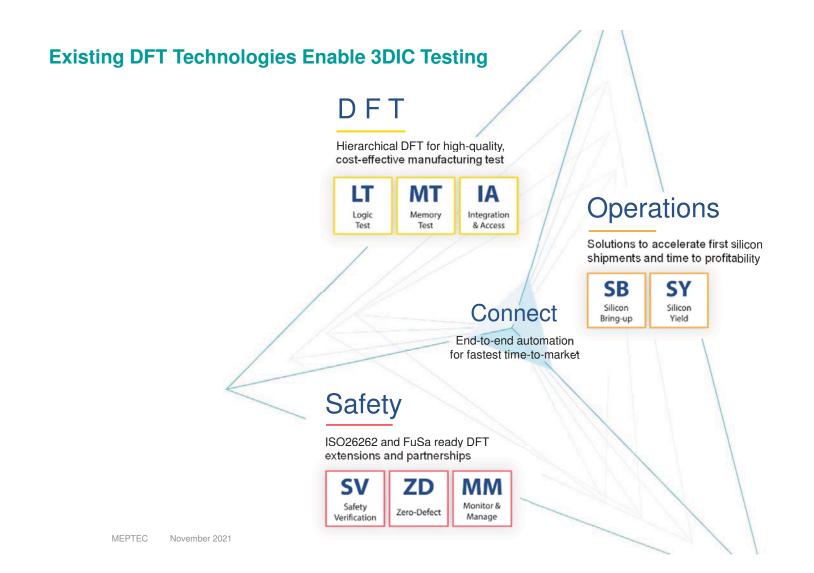

#### **Existing DFT Technologies Enable 3DIC Testing**

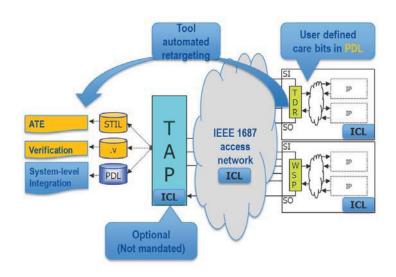

- Plug-and-play iJTAG infrastructure improves automation efficiency

- Universal method to integrate any IEEE 1687/1149.1 compliant IP

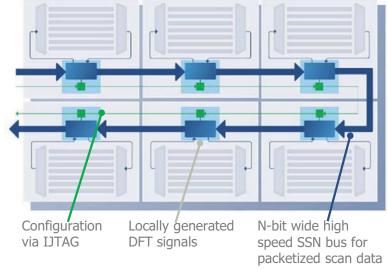

- Streaming scan network (SSN)

- -Save DFT development time

- Eases routing and timing closure

- Up to 4X test time and volume reduction

- -Low pin & low power

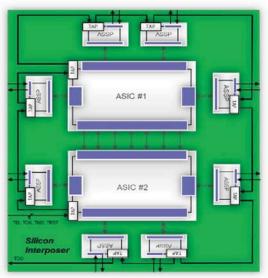

#### 2.5D DFT Methodology

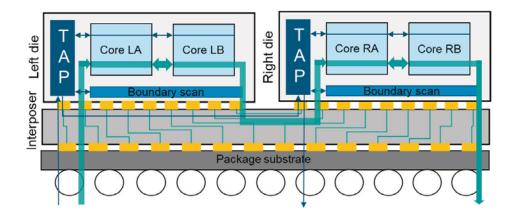

- 2.5D DFT infrastructure

- -2.5D 1149.1 compliant TAP

- Package-level BSDL for PCB test

- IJTAG support for IO BIST, PHY support

- 2.5D wafer-level die test

- Regular hierarchical DFT

- 2.5D die test in package

- Pattern re-targeting to package

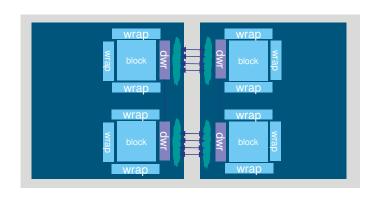

- 2.5D die-to-die test

- BSDL-based ATPG

- Interposer test utilizing die greybox based hierarchical DFT

**IEEE Standards** (i.e. 1149 specific)

**New DFT** Advancements

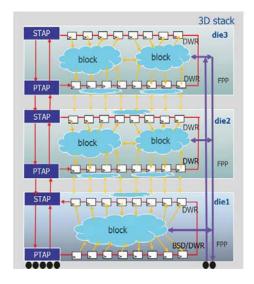

#### **3D DFT Methodology**

- 3D DFT infrastructure

- IEEE 1838 compliant TAPs & FPP using SSN

- 3D wafer-level die test

- Die wrapper register analysis and insertion

- -hierarchical DFT

- 3D die test in package

- Hierarchical DFT for pattern regarget

- -SSN broadcast to dies in package

- 3D die-to-die test

- ATPG based on package-level Verilog and graybox views of dies

- Multiple standards are needed

- -IEEE 1838, IEEE 1687, IEEE 1149.1/6/10, IEEE 1500 and etc

#### **Die to Die Test**

J. Reynick, Session 6C, VLSI Test Symposium, 2019

| Types                                         | Die IOs driven by BS Cells                                                                                                                          | Die IOs driven by wrap cells (logic between wrap cells and IOs)             |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| <ul><li>Low speed</li><li>Diagnosis</li></ul> | <ul><li>Pattern gen w/ die BSDLs as inputs</li><li>Diagnosis to be supported</li></ul>                                                              | <ul><li>D2D ATPG with low speed clock</li><li>Automatic diagnosis</li></ul> |

| <ul><li>At speed</li><li>Diagnosis</li></ul>  | <ul> <li>D2D atpg, or D2D snake test</li> <li>Clocks sync-up across dies w/ Tessent OCC</li> <li>Automatic diagnosis w/ at-speed pattern</li> </ul> |                                                                             |

| High speed                                    | <ul> <li>iJTAG hook up to custom SerDes IO BIST</li> </ul>                                                                                          |                                                                             |

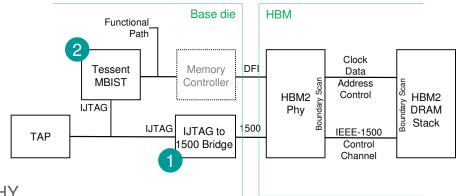

#### **External Memory HBM (e.g. HBM2) Support**

#### HBM2 comes with

- IEEE 1500 interface

- Embedded MBIST in HBM2 stack, operational through IEEE 1500 interface

-Other embedded features like IO repair

#### Two Memory BIST tasks

1 Connect to and operate the embedded HBM2 MBIST through the IEEE 1500 / IEEE 1687 integration

2 If desired, implement a MBIST to connect to the PHY

#### **3D IC Reference Flow and ITC Exposure**

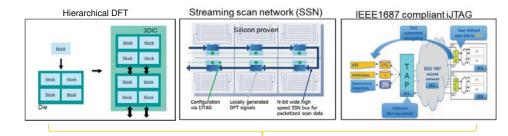

Siemens has also partnered with TSMC to build a Design for Testability (DFT) flow for TSMC's 3D silicon stacking architecture. Siemens' Tessent™ software provides a leading-edge DFT solution based on hierarchical DFT, SSN (Streaming Scan Network), enhanced TAPs (test access ports) and IEEE 1687 IJTAG (internal joint test action group) network technologies, all of which are IEEE 1838 compliant. Designed for scalability, flexibility and ease-of-use, the Tessent solution helps customers optimize resources associated with IC test technology.

#### SIEMENS

Plano, TX, USA, 26 October 2021

Siemens collaborates with TSMC on design tool certifications for TSMC's advanced technologies and other industry milestones

Ongoing callaboration with longtime foundry partner TSML has resulted in an array of new product certification, and that the companies have reched key milestones for cloud-enabled K design, as well a for TSMC 2DFabric, TSMC's comprehensive family of 3D silicon stacking and advanced packaging technologies:

Today at the TSMC 2021 Online Open Innovation Platform<sup>®</sup> (OIP) Ecosystem Forum, Siemens Digital Industries Software announced that ongoing collaboration with longitime foundry partner TSMC has resulted in an array of new product certifications, and that the companies have reached key milestones for cloud-enabled it design, as well as for TSMC 3DFabric<sup>®</sup>, TSMC's comprehensive family of 3D silicon stacking and advanced packaging technologies.

The Siemens EDA offerings recently certified for TSMC's N3 and N4 processes include the Calibre® nmPlatform, Siemens' industry-leading physical verification solution for IC sign-off, as well as the Analog

Siemens has also partnered with TSMC to build a Design for Testability (DFT) flow for TSMC's 3D silicon stacking architecture. Siemens' Tessent'' software provides a leading-edge DFT solution based on hierarchical DFT, SSM (Straming-Scan Network), enhanced TAP; fest access ports) and IEEE 1687 UTAG (internal joint test action group) network technologies, all of which are IEEE 1838 compliant. Designed for scalability, flexibility and ease-of-use, the Tessent solution helps customers optimize resources associated with IC test technology.

Siemens continues to increase its value to the TSMC OIP ecosystem by offering more features and solutions in support of our most advanced technologies," said 5uk Lee, vice president of the Design Infestructure Management Division at TSMC." We look forward to our continued collaboration with Siemens to help our mutual customers accelerate silicon innovations with design solutions combining Siemens' leading-edge electronic design automation (EDA) technologies with TSMC's latest process and 30Fabric technologies."

Finally, Siemens' close collaboration with TSMC recently enabled the Calibre tools to demonstrate dramatic performance and scaling improvements for one of the world's foremost IC design firms within a leading cloud computing environment. Made possible by the optimization of the latest setup, decks and engine technologies for doud environments within Calibre, these advancements can help giorist customers realize faster time-to-tapeout and time-to-market. To learn more, please make plans to view Siemens' technical presentation during the TSMC 2021 Online oil PE Goosytem Forum.

#### Conclusion

- 3DIC test solution built upon both existing technologies and new advancements

- Hierarchical DFT, SSN and IJTAG provide a solid foundation

- IFFF1838 hardware and lots of enhancements make 3D solution available

- 3DIC is a Moving Target

- Heterogeneous die support using different DFT vendor solutions

- Interposer test during stacking

- Redundant IO & lane and their repair requirements

- Call for an all-industry collaboration to enable 3DIC ecosystem for testing

- Build reference flows

- Define standard interface for die to die communication and data exchange if using different DFT vendor solutions

# Thank you sponsors!

# ADVANTEST®

SYNOPSYS®

# Amkor's Differentiators

### Technology

Advanced Packaging Leadership

Engineering Services

Broad Portfolio

## Quality

QualityFIRST Culture Execution Automation

### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

## Global Companies Rate Advantest THE BEST ATE Company 2021

Advantest receives highest ratings from customers in annual VLSIresearch Customer Satisfaction Survey for 2 consecutive years.

Global customers name Advantest THE BEST supplier of test equipment in 2020 and 2021, with highest ratings in categories of:

Technical Leadership – Partnership – Trust – Recommended Supplier – Field Service

"Year-after-year the company has delivered on its promise of technological excellence and it remains clear that Advantest keeps their customers' successes central to their strategy. Congratulations on celebrating 33 years of recognition for outstanding customer satisfaction."

— **Risto Puhakka**, President VLSIresearch

# SYNOPSYS®

Silicon to Software™

## **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Data & Test** (November 9-11, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org