## Road to Chiplets: Data & Test

November 9 - 11, 2021

# ML in Semiconductor Test (A "Balanced Approach")

#### Sergio Mier

Sr. Director, Digital Test Engineering Qualcomm Technologies, Inc.

### Outline

- Today's Challenges

- Existing and newly adopted test capabilities

- Offline & Test Case example

- Online and Test Case Example

- Tomorrow's opportunities

- Conclusions

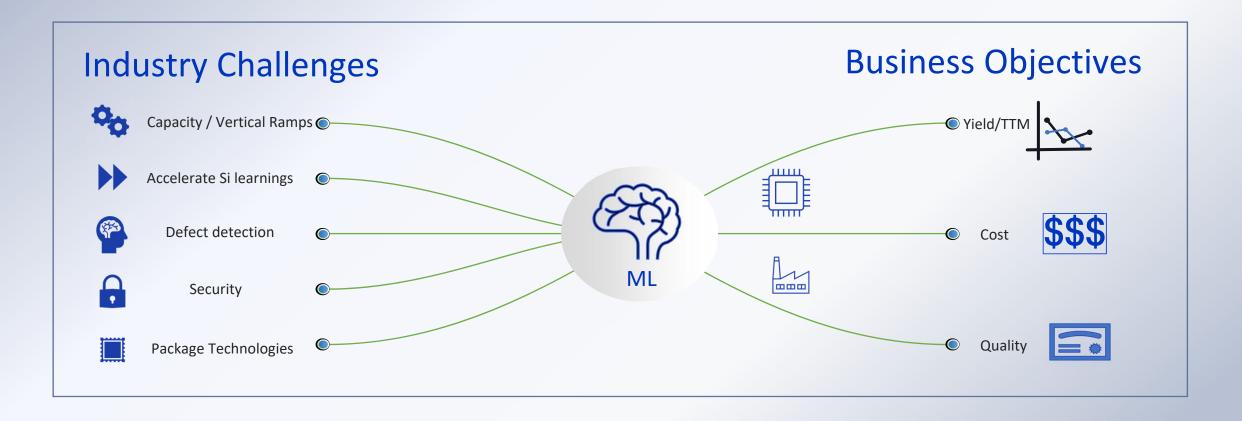

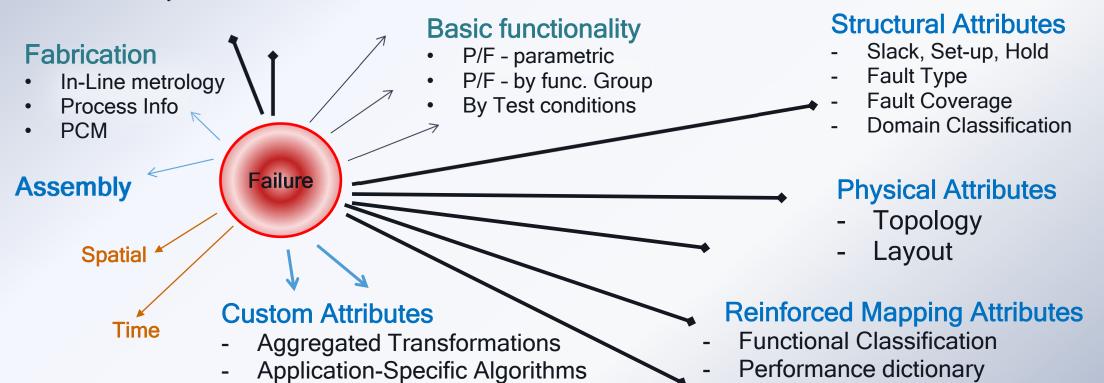

## Semiconductor Challenges - Overview

Can ML at the SOC level help address Business Challenges at the Chiplet Level?

Advanced Analytics & AI development will be significantly relied upon to accelerate the validation

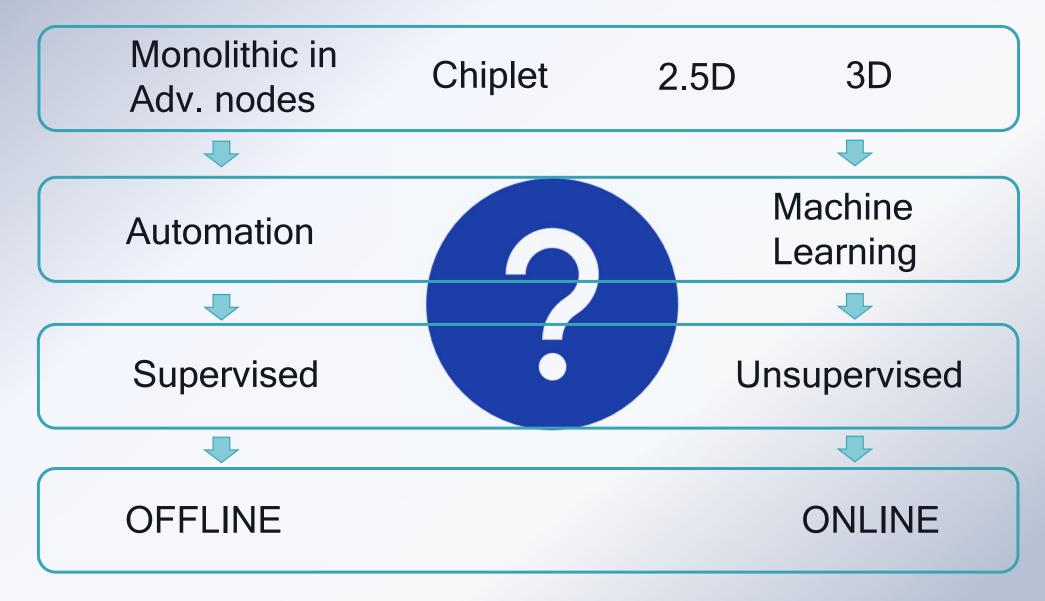

## Semiconductors' continuous evolution strategies

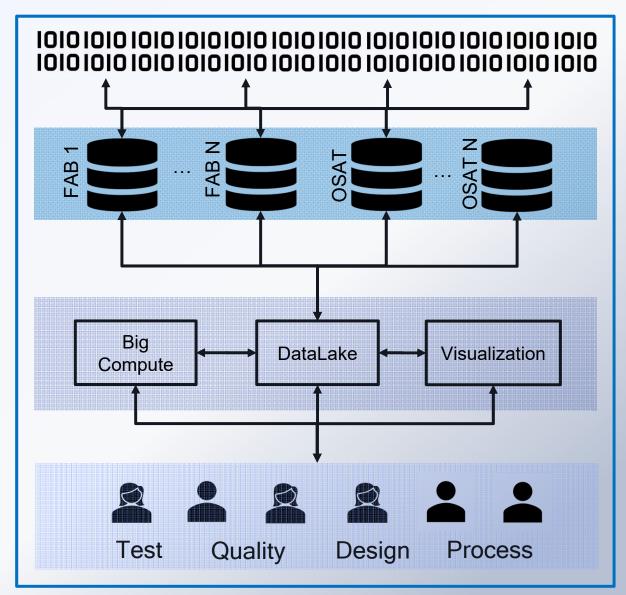

#### What's available: Offline Infrastructure

#### Benefits:

- ✓ Flexible compute power

- ✓ Scalable to multiple users / locations

- ✓ Secured

- ✓ Optimal for Training and Learning tasks

- ✓ Enables visualization & analysis tools

- ✓ Easy deployment of ML Models

#### Limitations

- ✓ Large Latencies ( secs/min/hrs/days )

- On-The-Fly inference High Cost impact

- Latency is directly proportional to the complexity

- Latency is directly proportional to # of models

- ✓ Security:

- Not a Zero-Trust solution for production

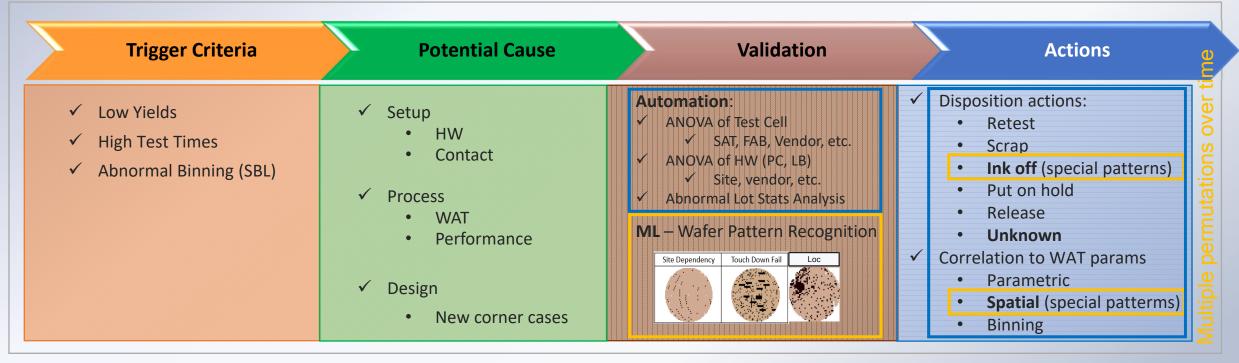

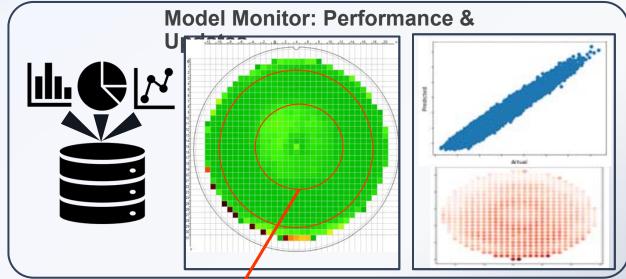

## The Offline Case: Lot Disposition Assistant

#### **Assisted Disposition: ML and Automation Improved Product Quality and Operational Efficiency**

- Improved disposition time by 10x with >95% accuracy

- Consistent performance on matured technologies nodes

- Enables test team with potential causes on the abnormal parameters

Automation + Machine Learning = Accelerated Benefits

#### Challenge: Maintenance required over time:

- Train models to include new wafer patterns over time

- Development of new Ink-off patterns to optimize yields

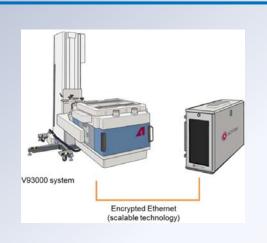

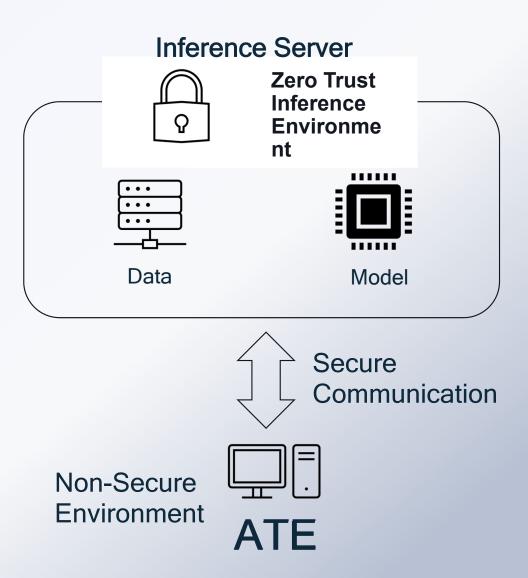

## What's getting adopted: Online Infrastructure ATE's Inference Server

#### Benefits:

- ✓ On-the-Fly ML Scoring /Decision Making

- ✓ Zero Trust Environment approved

- Secured ATE Communication (Encrypted)

- ✓ Minimum Latencies (uSec/mSec)

- ✓ Easy model integration with test program

#### Limitations

- ✓ Limited compute power

- ✓ Must have HW available at FABs/OSATs

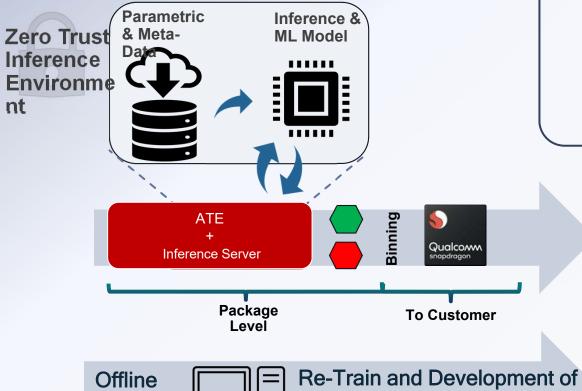

#### The Online Case: Parametric Predictions

#### How does it work?

| feature importance Param A 0.104327 Radius 0.098059 Param B 0.093004 Param C 0.090174 Test Time 0.081076 TouchDown # 0.072988 Param D 0.071371 Param E 0.064497 Param F 0.058431 GDBN 0.019612 | FEATURE                                                              | IMPORTANCE                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|

| Param C 0.090174 Test Time 0.081076 TouchDown # 0.072988 Param D 0.071371 Param E 0.064497 Param F 0.058431                                                                                    | Param A                                                              | 0.104327                                                             |

| GDBN 0.019012                                                                                                                                                                                  | Param C<br>Test Time<br>TouchDown #<br>Param D<br>Param E<br>Param F | 0.890174<br>0.881076<br>0.072988<br>0.071371<br>0.064497<br>0.058431 |

|                                                                                                                                                                                                | 00011                                                                | 0.017012                                                             |

#### **Benefits:**

- Param Test reduced by > 50%

- No Quality impact

- Extends beyond ATE APIs

- Can run multiple models in same project

- Identify performance matching ICs

- Negligible TT overhead

#### **Limitations:**

- Scalability of Inference HW over FAB /OSAT

- Limited adaptation over time

Compute

Improved ML model

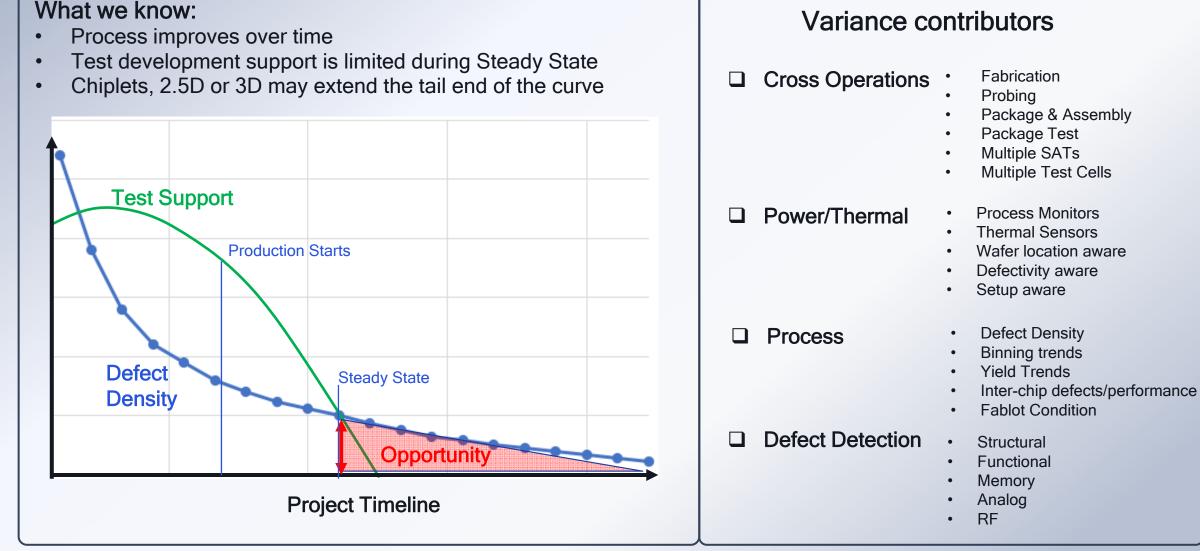

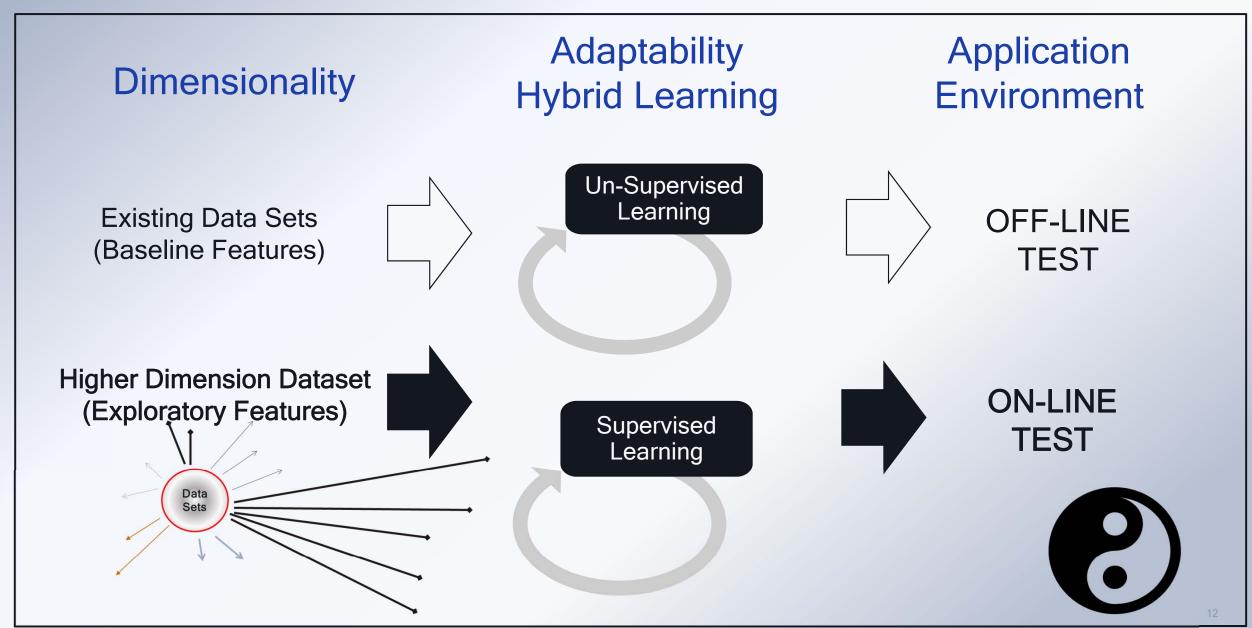

## The constant challenge: "Capable to adapt over time"

How to enable adaptability in our ML models?

#### Capture Variances with Higher Dimension Datasets

#### Collaboration across all disciplines → Strong Failure Signatures

#### **Aggregated Reactive Attributes**

- Failure Analysis

- Customer Returns

- Quality Excursions

#### **Enhanced Test Data at all Test Operations**

- Common Test Attributes across Wafer, SOC & Chiplet

- Test Attributes of both Good & Bad Device

What worked, didn't work

Qualcom

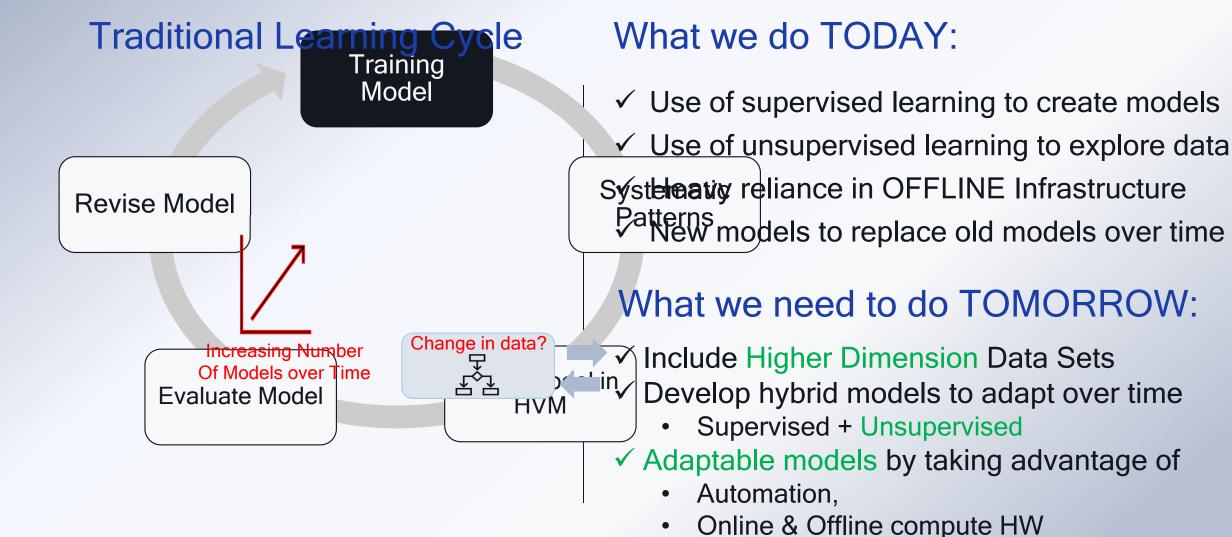

### Today's Strategy - tomorrow's opportunity

#### In the Not-So-Distant Future

Qualcomm Technologies, Inc.

### In Conclusion:

#### WHAT IS an extension of today's methodologies:

- Increased adoption of Automation + ML capabilities on Test Engineering

- Accelerate learnings w/process, package, etc.

- Reuse of sensors (+ New DFT) to analyze the impact of new package, process, design, d2d I/F, etc.

- Reuse of traditional SOC ML techniques applied to 2.5D, 3D & Chiplets products.

- Parallel paths for Supervised (Fast Execution) and Unsupervised (Fast Discovery) on-the-fly models

#### WHAT WILL be the next generation methodologies:

- Development of application specific sensors on HW from initial analysis / debug findings.

- EDA + ATE → Connecting Pre-silicon (planning) with Post-silicon (actuals) environments

- Chiplets, 2.5D & 3D will require new features to capture defect variances and adaptation over time

- Data Vendors → Minimum to no delay data transport time across test insertions

- ML HW test cells to offer a "Smart" cell environment

- ATE → Enable continuous learning and adapting capabilities ON-THE-FLY w/o impacting throughput

- Implementation of Hybrid Models to speed up exposure of new defects / performance degradation

- Across several TBs of data / day

#### Qualcomm

## Thank you

Follow us on: **f y** in **o**

For more information, visit us at:

www.qualcomm.com & www.qualcomm.com/blog

All data and information contained in or disclosed by this document is confidential and proprietary information of Qualcomm Technologies, Inc. and/or its affiliated companies and all rights therein are expressly reserved. By accepting this material the recipient agrees that this material and the information contained therein will not be used, copied, reproduced in whole or in part, nor its contents revealed in any manner to others without the express written permission of Qualcomm Technologies, Inc. Nothing in these materials is an offer to sell any of the components or devices referenced herein.

©2018-2021 Qualcomm Technologies, Inc. and/or its affiliated companies. All Rights Reserved.

Qualcomm and Snapdragon are trademarks or registered trademarks of Qualcomm Incorporated, registered in the United States and other countries. Other products and brand names may be trademarks or registered trademarks of their respective owners.

References in this presentation to "Qualcomm" may mean Qualcomm Incorporated, Qualcomm Technologies, Inc., and/or other subsidiaries or business units within the Qualcomm corporate structure, as applicable. Qualcomm Incorporated includes our icensing business, QTL, and the vast majority of our patent portfolio. Qualcomm Technologies, Inc., a subsidiary of Qualcomm Incorporated, operates, along with its subsidiaries, substantially all of our engineering, research and development functions and substantially all of our products and services businesses, including our QCT semiconductor business.

## Thank you sponsors!

## ADVANTEST®

SYNOPSYS®

## Amkor's Differentiators

#### Technology

Advanced Packaging Leadership

Engineering Services

Broad Portfolio

#### Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

#### Global Companies Rate Advantest THE BEST ATE Company 2021

Advantest receives highest ratings from customers in annual VLSIresearch Customer Satisfaction Survey for 2 consecutive years.

Global customers name Advantest THE BEST supplier of test equipment in 2020 and 2021, with highest ratings in categories of:

Technical Leadership – Partnership – Trust – Recommended Supplier – Field Service

"Year-after-year the company has delivered on its promise of technological excellence and it remains clear that Advantest keeps their customers' successes central to their strategy. Congratulations on celebrating 33 years of recognition for outstanding customer satisfaction."

— **Risto Puhakka**, President VLSIresearch

# SYNOPSYS®

Silicon to Software™

#### **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Data & Test** (November 9-11, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org