## Road to Chiplets: Data & Test

November 9 - 11, 2021

## **ADVANTEST**®

Ken Butler Strategic Business Creation Manager Advantest

All Rights Reserved - ADVANTEST CORPORATION

## Data Growth: The Tyranny of Numbers

For some time now, electronic man has known how 'in principle' to extend greatly his visual, tactile, and mental abilities through the digital transmission and processing of all kinds of information. However, all these functions suffer from what has been called 'the tyranny of numbers.' Such systems, because of their complex digital nature, require hundreds, thousands, and sometimes tens of thousands of electron devices.

Jack Morton, VP, Bell Labs, June 1958

**Jack Morton** NAE page

#### Fast forward to modern times

In 2014, semiconductor production facilities made 250 billion billion (250 x 10<sup>18</sup>) transistors. [2021 figure is 1.6x10<sup>21</sup>]. This was, literally, production on an astronomical scale. Every second of that year, on average, 8 trillion transistors were produced. That figure is about 25 times the number of stars in the Milky Way and some 75 times the number of galaxies in the known universe.

- Dan Hutcheson, CEO, VLSI Research, April 2015

#### How much test data does generate?

Assuming only 80% of the transistors are tested and each transistor results in just one bit of data, that is >40 Tb per second in 2021!

## **More Trends Challenging to Test**

| Trend                                 | Challenges                                                                                                                                   |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Growth in automotive sector           | <ul><li> "Zero defects" or parts or billion test escapes</li><li> Extended temperature operation</li><li> Reliability requirements</li></ul> |

| Manufacturing disaggregation          | <ul><li>Data movement and data sharing</li><li>Information/IP protection</li></ul>                                                           |

| Growth in machine learning/AI methods | <ul><li>Test time</li><li>IP protection</li></ul>                                                                                            |

| Advanced lithography                  | <ul><li>New defect mechanisms</li><li>Subtle failures</li></ul>                                                                              |

| On-premise to cloud-based solutions   | <ul><li>Data and IP protection</li><li>Analytics performance in some applications</li></ul>                                                  |

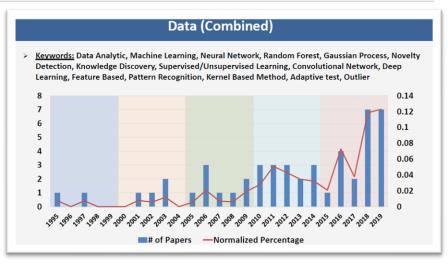

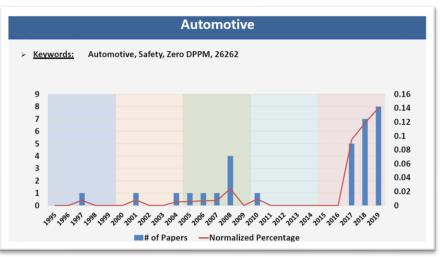

#### International Test Conf analytics papers

#### International Test Conf automotive papers

## **Chiplets Impact on Test and Data**

### Many aspects of test and data influenced by chiplet-based products

- Larger systems within a package the amount of test data goes up dramatically

- Known good die ensure that each chiplet is completely functional before integration

- Die traceability

- Debug, root cause analysis, and in some cases die matching

- Need improved collection and communication of origin of each chiplet

- Functional test content (not using design for test [DFT] structures) and system level test increasing

- Electrical failure analysis is more complex and data-intensive

- Need to migrate more test content earlier in the flow

- Detect defective units earlier prior to integration, decrease end of line yield loss

- Requires more correlation work to identify tests at wafer that detect downstream system level failures

## What Are Product Teams Asking For?

#### Some examples

- Adaptive e-test solution

- Optimize data collection at wafer parametric test

- Automate root cause analysis, increase throughput at e-test operation

- Real-time analytics, especially with ML workloads

- Speed up complex analytics

- Improve yield and quality while optimizing test cell utilization

- Rapid scan or other failure isolation

- Screening and real-time test solutions for automotive, other quality-sensitive products

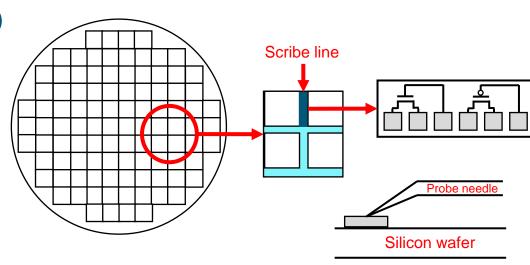

## What Exactly Is E-Test?

- A rose by any other name...E-Test, parametric test, wafer acceptance test (WAT)

- Primary objective: Discover root causes of device performance deviation

- Test structures in scribe lines between die on wafer

- Limited test of sites across wafer (e.g., 9 or 20 sites)

- **Challenge Minimize downtime, manual analysis** when out-of-spec measurements detected

Bhushan M., Ketchen M.B. (2015) Electrical Tests and Characterization in Manufacturing. In: CMOS Test and Evaluation. Springer, New York, NY.

https://doi.org/10.1007/978-1-4939-1349-7 7

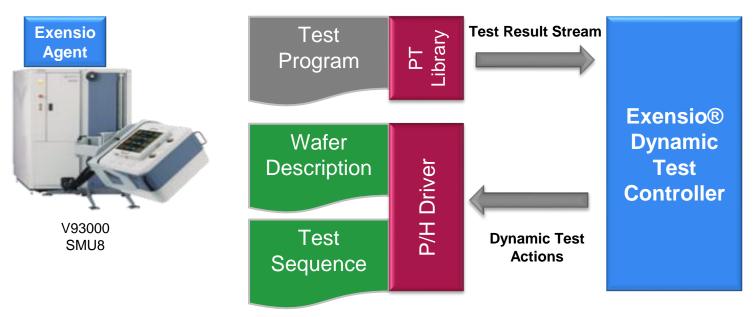

## **DPT: Dynamic Parametric Test**

- Exensio® from PDF Solutions is a portfolio of data analytic & storage products are integrated with the Advantest V93000/SMU8 parametric tester and PDF Solutions Exensio®

- DPT provides a Rules Engine, programmed by the customer, to redirect the wafer flow (test locations, algorithm, test plan) within milliseconds of a qualifying parametric test data point

- The objective is to optimize test time and problem-solving instantly with minimal human interaction required

- Exensio Evaluates Rules

- Modifies Test Flow

- Adjusts Test Algorithms

- 93K Executes New Test Recipe

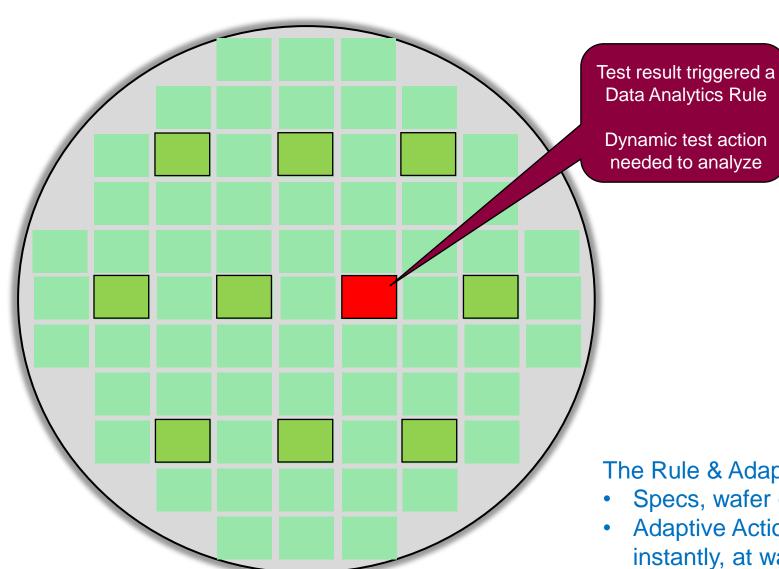

## **DPT Example: Diode Test, Measure VD @ ID = 100 nA**

V93000 Data Stream contents during a wafer measurement

| Die X-Y | <b>Measure</b> | Other Data |

|---------|----------------|------------|

| -2, 3,  | 0.642,         | XXX,       |

| 0, 3,   | 0.643,         | XXX,       |

| 2, 3,   | 0.644,         | XXX,       |

| -3, 0,  | 0.643,         | XXX,       |

| -1, 0,  | 0.644,         | XXX,       |

| 1, 0,   | 0.638,         | XXX,       |

| 3, 0,   | 0.643,         | XXX,       |

| -2, -3, | 0.642,         | XXX,       |

| 0, -3,  | 0.643,         | XXX,       |

| 2, -3,  | 0.644,         | XXX        |

The Rule & Adaptive Action could be based upon:

- Specs, wafer or lot statistics, process C<sub>pk</sub>, . . .

- Adaptive Action from Rule trigger could happen instantly, at wafer-end, or lot-end

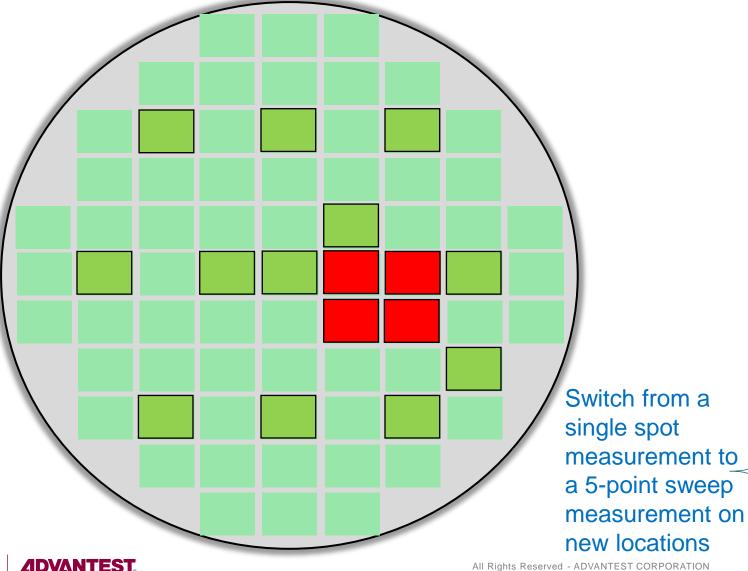

## Adaptive Test Action: Change from Spot to Sweep

#### **Original Spot Measurement Data**

| <u>Die X-Y</u> | <u>Measure</u> | (Spot)              |

|----------------|----------------|---------------------|

| -2, 3,         | 0.642,         |                     |

| 0, 3,          | 0.643,         |                     |

| 2, 3,          | 0.644,         |                     |

| -3, 0,         | 0.643,         |                     |

| -1, 0,         | 0.644,         |                     |

| 1, 0,          | 0.638,         |                     |

| 3, 0,          | 0.643,         | Poot cours          |

| -2, -3,        | 0.642,         | Root cause          |

| 0, -3,         | 0.643,         | isolated as         |

| 2, -3,         | 0.644,         | reticle/etch issue! |

#### **New Adaptive Test Flow**

(new test algorithms & die locations)

| Die X-Y | Measure | Sweep | ) |  |

|---------|---------|-------|---|--|

|         |         |       |   |  |

| 0, 0,  | 0.643, 0.584, 0.524, 465, 405,     |

|--------|------------------------------------|

| 1, 1,  | 0.642, 0.583, 0.523, 464, 405,     |

| 2, 0,  | 0.638, 0.578, 0.519, 0.459, 0.400, |

| 2, -1, | 0.639, 0.579, 0.520, 0.460, 0.401, |

| 1, -1, | 0.639, 0.580, 0.520, 0.461, 0.401, |

| 3, -2, | 0.642, 0.583, 0.524, 0.465, 0.405, |

## **Adaptive Test and Real-Time Analytics During Test**

- Production test has traditionally been performed as "one size fits all" approach

- Inefficient use of valuable test resources, especially vis à vis natural material variation

- A better approach is to adapt the test flow, contents, limits, etc., to the material at hand

- Example use cases

- Optimize looped tests which search for minimum voltage, maximum frequency, etc.

- Use predictive analytics to optimize device tuning/trimming

2019 DATE Conf. V<sub>MIN</sub> search limits prediction

2021 VLSI Test Symp. Trim solution prediction

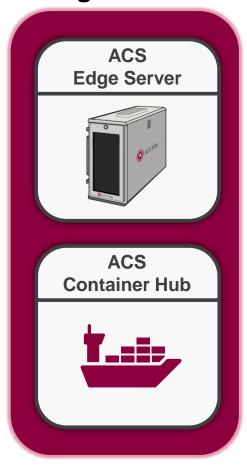

## **ACS Edge**

#### **ACS Edge Core Product**

A real-time, securityfirst, cloud connected high performance test cell compute solution

An industry-first, developer centric approach to secure deployment of algorithmic workloads in semiconductor test

#### **ACS Edge Extensions\***

Integrated Data Feed Forward/Backward, for complex data-science using other insertion data on demand.

Pre-built solutions, fully vetted and qualified for some of the most complex challenges in semiconductor test

Integrated monitoring of systems and workloads, to improve OEE and diagnose workloads

\* Some extensions not available at launch

## Success Stories from Two of the Top5 fabless companies

#### Large Fabless 1

- Large fabless complex digital SoC customer who uses ACS Edge for complex machine learning inferences for dynamic retest.

- TensorFlow 2.0 base ML container

- Initial validation & PoC on three-lab based systems in ~2 months

- Successful roll-out to Taiwan-based test house, loading large number of production systems ~6 months

- Initial cost savings estimate due to improved yield > \$10's of M / year

#### **Large Fabless 2**

- Large fabless complex digital GPU customer who uses ACS Edge for complex machine learning inferences for tiered binning.

- PyTorch ML container

- GPU accelerated ACS Edge version (NVIDIA T4)

- Initial validation & PoC phase at Engineering Lab & NPI in Taiwan-based test house

- Customer is reliably able to bin additional premium bin & value tier without increase in CoT

- Production roll-out planned for late 2021

## Other Challenges: Data Integration

Breaking down silos

"Fail Silo" by thetorpedodog is licensed under CC BY-SA 2.0

To truly meet the need for end-to-end solutions, data must be integrated from widely varying sources

- Recent example: Prediction of burned wafer probe needles

- Multiple potential root causes many places to look

- Data often siloed challenging to tie together for a given product

- Electronic chip ID (ECID) commonplace for digital SoCs, but is non-standard, different for each company

|                       |                                                                                                                                                                                                               | Fall Silo by thetorpedodog is licensed under <u>CC BY-SA 2.0</u>                                                                                                    |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data origin           | Types of data                                                                                                                                                                                                 | What to look for                                                                                                                                                    |

| Wafer probe/test cell | <ul> <li>Maintenance records</li> <li>Inspection</li> <li>Probe test</li> <li>Calibration</li> <li>On-die parametrics</li> <li>Z-travel and contact force</li> <li>Thermal sensors</li> <li>Alarms</li> </ul> | <ul> <li>Timing of probe burn events</li> <li>Calibration issues</li> <li>Equipment issues</li> <li>Warping of wafers, boards</li> <li>Localized heating</li> </ul> |

| Wafer fab             | <ul><li> Equipment</li><li> Inspection</li><li> In-line scribe test</li></ul>                                                                                                                                 | <ul><li>Misprocessing</li><li>Hot/cold material</li></ul>                                                                                                           |

| Board shop            | <ul><li>Repair records</li><li>Board images</li></ul>                                                                                                                                                         | Failing probe counts, locations                                                                                                                                     |

| Design IT             | <ul><li>Chip layout</li><li>Power grid layout</li><li>Chip power sims/analysis</li><li>On-die sensors</li></ul>                                                                                               | <ul><li>Low pin count power planes</li><li>Localized heating</li></ul>                                                                                              |

| Test IT               | <ul><li>Program content</li><li>Program release artifacts</li></ul>                                                                                                                                           | <ul><li>Stress test content</li><li>Current/power spikes</li><li>Incorrect limits/clamps</li></ul>                                                                  |

### **Conclusions**

- Data creation, diversification growing at an exponential rate

- Test plays a central role in harvesting IC data to feed the entire value chain

- Chiplet-based products are among the most data-intensive

- Quality requirements increasing, especially in key sectors such as automotive

- Drives need for advanced techniques to identify at-risk units

- Machine learning use becoming commonplace at all phases in the product lifecycle

- IC supply chain is disaggregated → data still must be shared securely while protecting IP

- Our industry is responding with innovative solutions it's an exciting time to work in data science

"Data Nerds at the Tower @jeanong75 @vidasioson haha #Awesome2013 by The Pageman is licensed under CC BY-SA 2.0

## Acknowledgements

We acknowledge numerous contributions to this effort

#### **Advantest**

- Dave Armstrong

- Sonny Banwari

- Brent Bullock

- Brian Buras

- Dave Edwards

- Alan Hart

- Amit Kucheriya

- Raphaël Latty

- Ira Leventhal

- Benjamin Lobmüller

- Yichuan Lu

- Don Ong

- Keith Schaub

- Hui-Liang Wu

- Constantinos Xanthopoulos

#### **PDF Solutions**

- Greg Prewitt

- Vishnu Rajan

- Andreas Schmidt

- Thomas Zanon

## **ADVANTEST**®

Thank you!

Questions?

## Thank you sponsors!

## ADVANTEST®

SYNOPSYS®

## Amkor's Differentiators

## Technology

Advanced Packaging Leadership

Engineering Services

Broad Portfolio

## Quality

QualityFIRST Culture Execution Automation

#### Service

Design & Test Through Drop Ship

Manufacturing Footprint

Local Sales & Support

## Global Companies Rate Advantest THE BEST ATE Company 2021

Advantest receives highest ratings from customers in annual VLSIresearch Customer Satisfaction Survey for 2 consecutive years.

Global customers name Advantest THE BEST supplier of test equipment in 2020 and 2021, with highest ratings in categories of:

Technical Leadership – Partnership – Trust – Recommended Supplier – Field Service

"Year-after-year the company has delivered on its promise of technological excellence and it remains clear that Advantest keeps their customers' successes central to their strategy. Congratulations on celebrating 33 years of recognition for outstanding customer satisfaction."

— **Risto Puhakka**, President VLSIresearch

# SYNOPSYS®

Silicon to Software™

## **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **Road to Chiplets: Data & Test** (November 9-11, 2021). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org