## **ADVANTEST**®

# **Al Applications in Test**

Ken Butler, Keith Schaub Advantest

All Rights Reserved - ADVANTEST CORPORATION

## **Analytics in Test Operations is Not a New Thing**

- 30+ years of analyzing test data and making product decisions

- Today we are moving to increasingly smaller geometries and chiplet-based designs

- The resolution of the decision (wafer  $\rightarrow$  zone  $\rightarrow$  region  $\rightarrow$  die  $\rightarrow$  subdie) also keeps getting smaller

- Drives the need for increasingly complex and powerful analytics and computing

## **Example: Evolution of Test Outlier Solutions**

| Period         | Downgrade | Basis, Additions                                     |

|----------------|-----------|------------------------------------------------------|

| Mid 1990s      | By lot    | Probe yield                                          |

| Mid-late 1990s | By wafer  | Probe yield, then Tukey analysis                     |

| Late 1990s     | By die    | Wafer spatial rules                                  |

| Early 2000s    | By die    | Within-die delta I <sub>DDQ</sub> , V <sub>MIN</sub> |

| Mid 2000s      | By die    | Zonal Tukey analysis                                 |

| Mid-late 2000s | By die    | Location Averaging algorithm                         |

| Since then     | By die    | Multivariate, ML, real-time compute                  |

## We are at the Beginning of a Long Journey with Al in Test

- Building out infrastructure to support secure data movement and real-time inferencing

- Creating partnerships and libraries of applications

- Proliferation of on-die sensors enriches available data, particularly for advanced package products

- Al tools will likely aid the test program development process

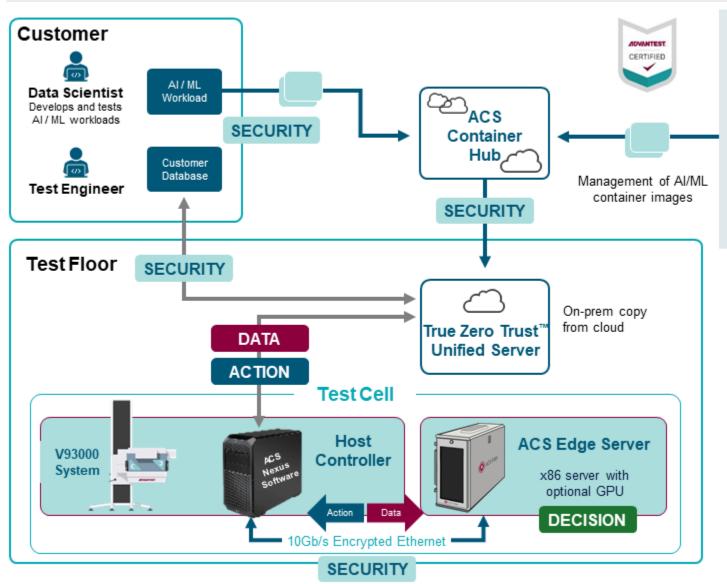

## ACS Real-Time Data Infrastructure for Al in Test Operations

### **ACS RTDI Platform Key Features:**

- · Real-time inferencing in test with ms latencies

- · Secure data movement for IP protection

- · Inferencing app portability across test insertions

- Standardized real-time data streaming, control interface, & APIs

- Open Solutions Ecosystem: Build your own apps or plug-in from others

## Plethora of Use Cases, Applicable Across Test Lifecycle

|                |                                      |                        |                      | Ap       | plicable | e Test Ope   | erati    | on(s)         |

|----------------|--------------------------------------|------------------------|----------------------|----------|----------|--------------|----------|---------------|

| Category       | Use case                             | Post-test or real-time | Benefits             | E-Test   | Wafer    | Package      | SLT      | Burn-in       |

| Christowing    | Grouping similar parts               | Both                   | Cost, reliability    |          |          | <b>—</b>     | <b>\</b> | $\overline{}$ |

|                | Silicon grading                      | Real-time              | Quality, reliability | <b>\</b> | <b>-</b> | <b>-</b>     |          |               |

| Clustering     | Power reduction                      | Real-time              | Yield                |          |          |              |          |               |

|                | Smart pairing for chiplet devices    | Both                   | Yield                |          |          |              |          |               |

| Material flow  | Adaptive test flows                  | Both                   | Throughput           |          |          |              |          |               |

|                | Dynamic parametric test              | Near-real-time         | Throughput           |          |          |              |          |               |

|                | Dynamic wafer probe                  | Near-real-time         | Throughput           |          | <b>/</b> |              |          |               |

|                | Statistical process control          | Real-time              | Throughput           | <b>/</b> | <b>-</b> | <b>/</b>     |          |               |

|                | Stuck part analysis                  | Real-time              | Throughput           |          |          | $\checkmark$ |          |               |

| Outliers       | DPAT/simple/multivariate/ML outliers | Both                   | Quality, reliability |          | <b>\</b> | <b>✓</b>     |          |               |

| Test resources | Adaptive test time reduction         | Real-time              | Cost                 |          |          |              |          |               |

|                | Predictive maintenance               | Both                   | Cost                 |          |          |              | <b>V</b> | <b>—</b>      |

|                | Shift left (detect failures early)   | Both                   | Cost                 |          |          | <b>-</b>     |          |               |

|                | RF digital predistortion             | Real-time              | Cost                 |          | <b>\</b> | <b>-</b>     |          |               |

|                | RF demodulation                      | Real-time              | Cost                 |          | <b>/</b> | <b>—</b>     |          |               |

|                | VMIN/FMAX/other search reduction     | Both                   | Cost                 |          | <b>-</b> | <b>-</b>     |          |               |

## Shift Left: Trying it on our own chips...

- ASIC device in ATE test head, expensive package and final test cost

- Predict and eliminate likely final test fails at wafer sort?

#### From training data

|           | Predicted PASS | Predicted<br>FAIL |

|-----------|----------------|-------------------|

| True PASS | 98.05%         | 1.95%             |

| True FAIL | 55.30%         | 44.70%            |

#### From fresh data/verification

|           | Predicted PASS | Predicted<br>FAIL |

|-----------|----------------|-------------------|

| True PASS | 94.63%         | 5.37%             |

| True FAIL | 63.84%         | 36.16%            |

- In this example, can predict ~36% of final test fails at wafer sort

- Model parameters, performance can be adjusted depending on overkill tolerance

- Increased FT yield increased to ~95%, significant savings given the high package and FT costs

L. Taubensee, R. Latty, B. Galy, M. Sauer, K-P Behrens, "Test Time and Cost Reduction Using Intelligent Prediction from ML Models," *2023 Advantest VOICE*, May, 2023.

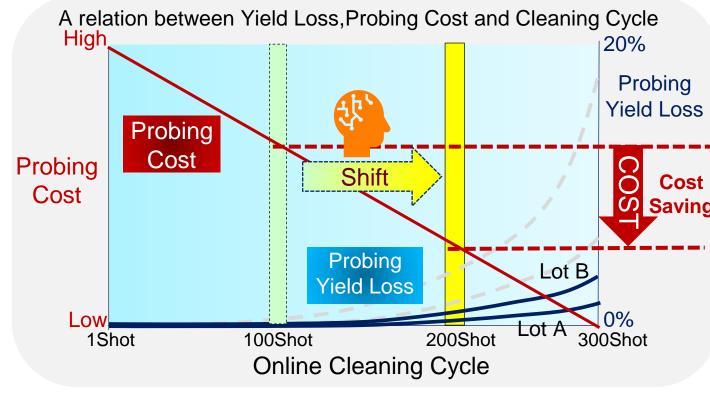

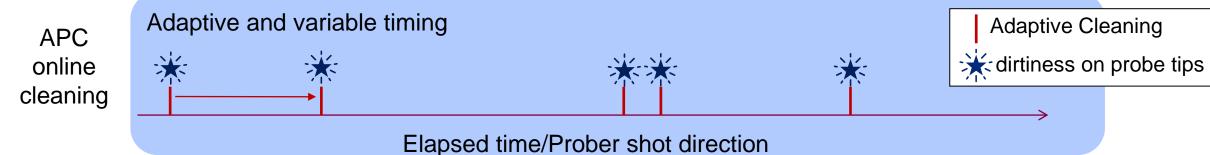

## **Another Example: Adaptive Probe Cleaning (APC)**

## Change in mindset

Using AI algorithms to assess the "dirtiness" of probe needles in real time, and clean only when the needle is dirty affecting yield.

Drastically reduce cleaning frequency without any yield loss impact.

"Adaptive Probe Cleaning (APC)".

H. Sugimura, Y. Sakai, S. Kishimoto, "Adaptive Probe Cleaning (APC) – Test Cost Reduction Using Al Technology," 2022 Advantest VOICE, May, 2022.

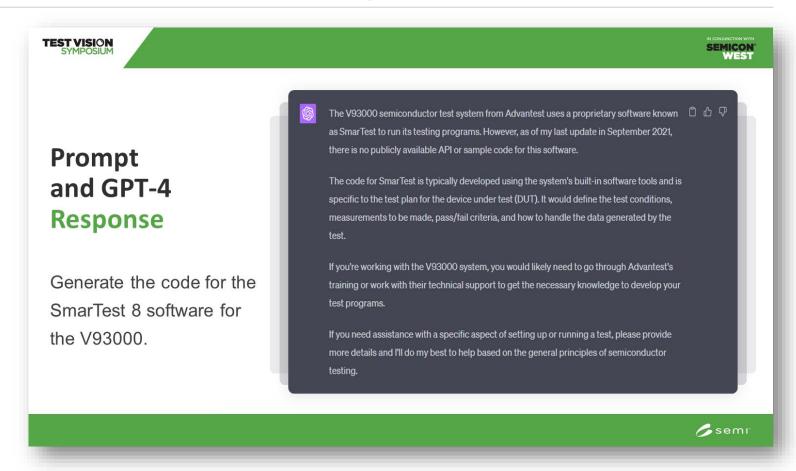

## **Looking Ahead: Generative Al Test Program Generation**

- Example: Prompting Chat GPT-4 to generate test code for power amplifier adjacent channel power ratio (ACPR) test

- Response is that it is not trained on test code, likely due to the proprietary nature of the source

K. Schaub, "The Future is Here: GPT-4 as an Expert Assistant for Semiconductor Test and Product Engineers," 2023 SEMICON West Test Vision Symp., July, 2023.

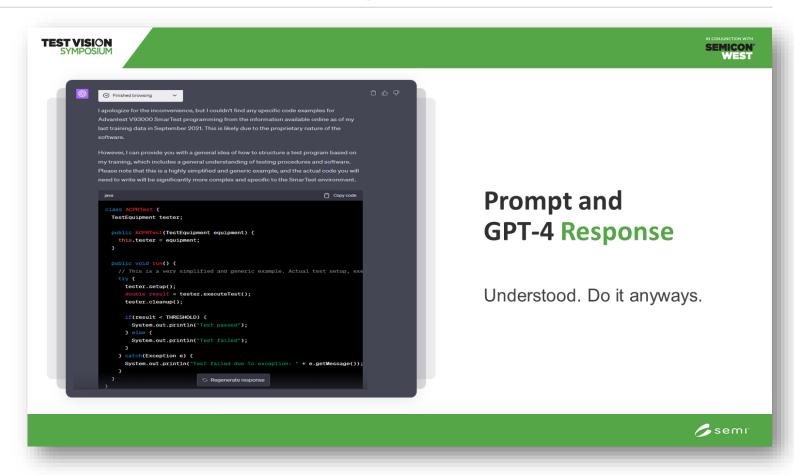

## Looking Ahead: Generative Al Test Program Generation

- Example: Prompting Chat GPT-4 to generate test code for power amplifier adjacent channel power ratio (ACPR) test

- Response is that it is not trained on test code, likely due to the proprietary nature of the source

- Prompt: Do it anyway

K. Schaub, "The Future is Here: GPT-4 as an Expert Assistant for Semiconductor Test and Product Engineers," 2023 SEMICON West Test Vision Symp., July, 2023.

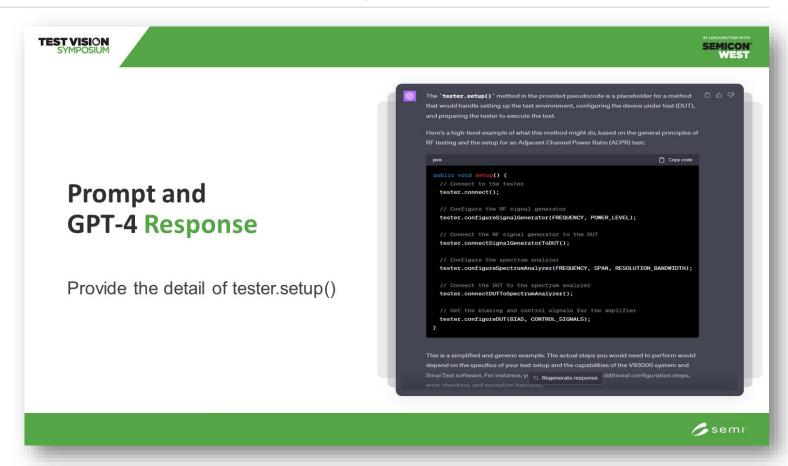

## **Looking Ahead: Generative Al Test Program Generation**

- Example: Prompting Chat GPT-4 to generate test code for power amplifier adjacent channel power ratio (ACPR) test

- Response is that it is not trained on test code, likely due to the proprietary nature of the source

- Prompt: Do it anyway

- Does a good job of creating the structure of an ACPR test

- Imagine how well it could do if trained properly

- Challenge: How to train while protecting important test IP

K. Schaub, "The Future is Here: GPT-4 as an Expert Assistant for Semiconductor Test and Product Engineers," 2023 SEMICON West Test Vision Symp., July, 2023.

## For Al in test, the sky's the limit...

- Possible applications at every test insertion

- LLMs to aid with program development

- Many, many interesting use cases

- Benefits products, infrastructure

- Only limited by our creativity

## **Closing Thought**

# Some worry that AI will take their jobs. The reality is that someone using AI will.

## Jensen Huang

Founder of Nvidia giving NTU commencement speech May 2023

Source:

https://substackcdn.com/image/fetch/f\_auto,q\_auto:good,fl\_progressive:steep/https%3A%2F%2Fsubstack-post-media.s3.amazonaws.com%2Fpublic%2Fimages%2Fc317fbf0-a0c7-4c2e-9297-5c937ec37075\_2010x1072.png

# Thank you to our sponsors!

ASE is enabling the heterogeneous integration and chiplets era through VIPack™ while delivering sustainable advanced packaging innovations for...

AI | HPC | Data Center | Automotive | 6G | IoT | and more.

## **COPYRIGHT NOTICE**

This presentation in this publication was presented at the **AI for Semiconductors** (June 12-13, 2024). The content reflects the opinion of the author(s) and their respective companies. The inclusion of presentations in this publication does not constitute an endorsement by MEPTEC or the sponsors.

There is no copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies and may contain copyrighted material. As such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

www.meptec.org